International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 11 Issue: 04 | Apr 2024 www.irjet.net p-ISSN: 2395-0072

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 11 Issue: 04 | Apr 2024 www.irjet.net p-ISSN: 2395-0072

1Department of Electronics and Communication Engineering, BMS College of Engineering, Bangalore, India

2Department of Electronics and Communication Engineering, BMS College of Engineering, Bangalore, India

Abstract - Understanding and optimizing JPEG decoding is imperative for several reasons. JPEG ubiquity in digital media from online content delivery to medical imaging underscores its significance. Balancing quality and speed are essential, impacting user experience in applications like online streaming and professional photography The study of JPEG decoding also contributes to storage efficiency, minimizing requirements and optimizing data transfer times. This article presents a “JPEG Decoder” which can deal with different quality of images that can be displayed on the screen with less loss of information and providing best storage capabilities and thereby increasing the overall performance of the Decoder. Overall, the articles achieved significant improvements in resource utilization. The optimized utilization of Slice LUTs and Slice Registers reflects a more judicious use of logic elements Slice LUTs (26.65%) and Slice Registers (8.06%), contributing to a streamlined and powerful logic implementation compared with [2] higher Slice LUT utilization (33.26%) and slightly increased Slice Register usage (8.44%). The efficient management of DSP resources underscores the design's computational capabilities, particularly in digital signal processing applications.

Key Words: FPGA,VGAController,ImageProcessing,XilinxVivado,Verilog.

1.INTRODUCTION

The evolution of JPEG decoding isintricatelywovenintothefabric ofdigital image processing,showcasing a remarkable journeythroughtechnologicaladvancementsandinnovativemethodologies.Aswetracethehistoricaltrajectory,wewitness thesteadyrefinementofJPEGdecodingalgorithms,drivenbytheincreasingdemandforefficientimagereconstruction.The inceptionoftheJPEGstandardcanbetracedbacktothelate1980swhentheJointPhotographicExpertsGroup(JPEG)was formed,comprisingexpertsfromvariousfieldsaimingtoestablishastandardizedimagecompressionmethod.Theresultwas thecreationoftheJPEGstandardin1992,whichquicklygainedwidespreadadoptiondue toitsabilitytostrikeabalance betweencompressionratiosandacceptableimagequality.

TheinitialJPEGdecodingalgorithmswereprimarilyimplementedongeneral-purposeprocessors,leveragingthecomputing poweravailableatthetime.However,asdigitalimageryproliferatedacrossdiverseapplications,thedemandforfasterand moreefficientdecodingprocessesintensified.TheintegrationofField-ProgrammableGateArrays(FPGAs)intoJPEGdecoding marked a significant turning point in the pursuit of enhanced performance. FPGAs, with their reconfigurable nature and parallelprocessingcapabilities,offeredacompellingalternativetotraditionalprocessors.Thisadaptabilityalloweddevelopers to tailor hardware architectures specifically for JPEG decoding, unlocking the potential for accelerated and optimized processing.ThesynergybetweenJPEGdecodingandFPGAtechnologygainedprominenceinvariousapplications,fromrealtimevideoprocessingto embeddedsystems.TheadaptabilityofFPGAsallowedfortailoredsolutionsthataddressedthe uniquechallengesposedbyJPEGdecoding,suchascomputationalintensityandreal-timeprocessingrequirements.

Inthecontemporarylandscape,theintegrationofFPGAtechnologyintoJPEGdecodingprocessescontinuestobeanareaof activeresearchanddevelopment.ThishistoricaljourneysetsthestageforourexplorationintotheintricaciesofJPEGdecoding, withaspecificfocusonleveragingFPGAaccelerationtoenhanceefficiencyandmeetthedemandsofmodernapplications. UnderstandingandoptimizingJPEGdecodingisimperativeforseveralreasons.JPEG’subiquityindigitalmediafromonline contentdeliverytomedicalimagingunderscoresitssignificance.Balancingqualityandspeed areessential,impactinguser experienceinapplicationslikeonlinestreamingandprofessional photography.As emerging technologies(virtual reality, augmentedreality)demandefficientimageprocessing,optimizedJPEGdecodingbecomespivotal.Usersatisfactionincontexts suchaswebbrowsingandmobileapplicationshingesondecodingspeed.IntegratinghardwareacceleratorslikeFPGAsoffers opportunitiesforsignificantperformanceenhancements.

Asdigitalimagerycontinuestoproliferateacrossdiversedomains,frommultimediastreamingtomedicalimaging,theability todecodecompressedimagesswiftlywhilemaintainingoptimalqualityhasemergedasacriticalchallenge.Attheheartofthis challengeliestheJPEGcompressionstandard,acornerstoneintherealmofimagecompression.Thisthesiscentersitsfocuson theintricateprocessofJPEGdecoding,unravelingthelayersthatconstitutethepost-compressionreconstructionofimages.A keymotivationistodelveintotheintricaciesofJPEGdecoding,withadualobjective:toenhancetheefficiencyofthedecoding processandtoexploretheintegrationofField-ProgrammableGateArrays(FPGA)asacatalystforaccelerateddecoding.JPEG

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 11 Issue: 04 | Apr 2024 www.irjet.net p-ISSN: 2395-0072

decoding,whilefoundational,canbecomputationallyintensive,especiallywhendealingwithhigh-resolutionimagesorrealtimeapplications.Toaddressthis,weturnourattentiontoFPGAtechnology aversatilehardwareplatformknownforits parallelprocessingcapabilities.ByharnessingtheinherentparallelismofFPGAarchitectures,weaimtodesignandimplement a high-performance JPEG decoding accelerator. The integration of FPGA into the decoding pipeline promises not only to expeditetheprocessbutalsotoprovideascalablesolution.Adaptabletovaryingcomputationalrequirements.Moreover,as thevolumeandresolutionofdigitalimagessurge,theroleofstorageinfacilitatingseamlessdecodingbecomesincreasingly crucial.

Thisthesisrecognizesthesymbioticrelationshipbetweendecodingspeedandstorageaccesstimes,emphasizingtheneedfora holisticapproach.Consequently,asignificantportionofthisresearchisdedicatedtoexploringstorageoptimizationtechniques, includingefficientdatastructures,andcachingmechanisms,tofurtheraugmenttheoverallperformanceofJPEGdecoding. Henceimageprocessingisoneofthefirststeptoobtaingoodqualityimageswithlessstoragerequired.Inourproposedwork wehavedevelopeda“ImageProcessingforOnScreenDisplay”whichcandealwithdifferentqualityofimagesthatcanbe displayedonthescreenwithlessloosofinformationandprovidingbeststoragecapabilitiesandtherebyincreasingtheoverall performanceoftheDecoder

Need for Lossy Decompression technology: In the context of real-time image and video processing using FPGA (FieldProgrammable Gate Array), the choice of lossy decompression remains pertinent due to the FPGA's parallel processing capabilitiesandthespecificdemandsofreal-timeapplications.FPGA-basedsystemsoftenprioritizecomputationalefficiency, andlossycompressionmethodsalignwellwiththeserequirements.JPEG,forinstance,isawidelyusedlossycompression standardthatcanbeimplementedefficientlyonFPGAplatforms.LossydecompressiononFPGAsallowsforrapidprocessingof compressedimageorvideodata,makingitsuitableforapplicationssuchasreal-timevideostreaming,surveillance,ormedical imaging,wherequickanalysisandresponsearecritical.

TheparallelprocessingnatureofFPGAsallowsforthesimultaneousdecompressionofmultipleframesorregions,contributing toreducedlatencyandimprovedthroughput.WhileFPGA-basedsystemsareknownfortheirhardwareaccelerationcapabilities, theyarestillsubjecttoresourceconstraints,includinglimitedon-chipmemoryandbandwidth.Lossycompressionmethods strikeabalancebetweenachievingcompressionefficiencyandminimizingresourceutilization,makingthemwell-suitedfor FPGAimplementationsinrealtimeimageandvideoprocessingscenarios

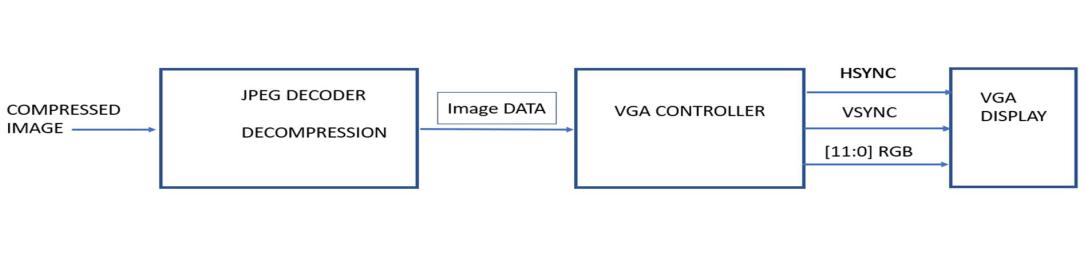

We observed there is a need of processing unit where it can process the compressed image efficiently with improved performance,clarityoftheimageandoccupieslessstorageFig-2showstheproposedblockdiagramforJPEGDecoder

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 11 Issue: 04 | Apr 2024 www.irjet.net p-ISSN: 2395-0072

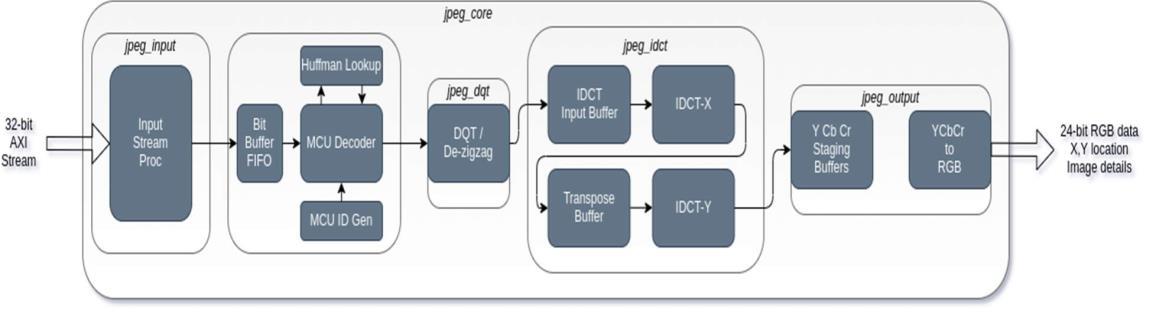

Description of Processing in each step:

JPEG Input:

Thisiswheretheprocessbegins.ItrepresentsaninputstreamofJPEGimages.

Input Stream Proc:

Thisstephandlestheinitialprocessingoftheinputstream.Itpreparesthedataforfurtherstages.

MCU Decoder:

MCUdecodethecompressedimagedata,extractMCUs,performHuffmandecoding,andgenerateidentificationinformationfor properarrangementduringtheimagereconstructionprocessinaJPEGdecoder.

JPEG_DQT Block:

TheJPEG_DQTblockplaysapivotalroleintheJPEGdecodingprocessbyde-quantizingthecoefficientsandreversingthezigzag orderingappliedduringcompression.Thispreparesthedataforthesubsequentstages,suchasIDCT,wheretheoriginalimage dataisreconstructed.

JPEG-IDCT block:

TheJPEG_IDCTblockisresponsibleforreversingtheeffectoftheDiscreteCosineTransformappliedduringJPEGcompression.

JPEG Output:

TheJPEG_OutputblocktakestheYCbCrimagedataobtainedfromtheJPEG_IDCTblock,stagesitinseparatebuffers,andthen performstheYCbCrtoRGBcolorspaceconversion.

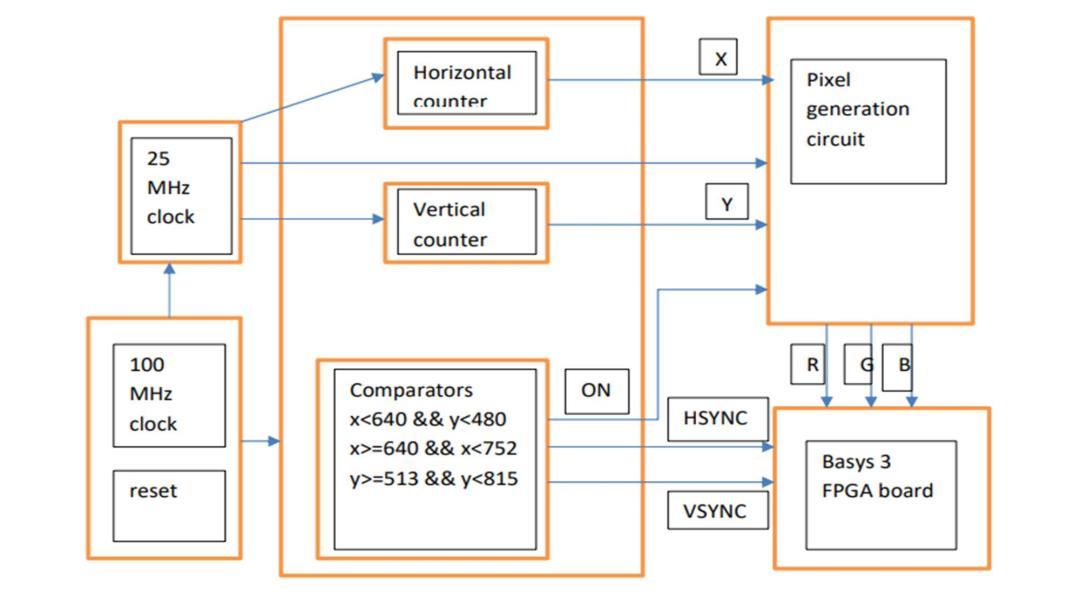

2.2 Implementation of VGA Controller:

TheVGAcontrollerdesignfollowsamodularapproach,withtwomainmodules:`vga_test`and`vga_controller`.The`vga_test` moduleservesasthetop-levelmoduleandinstantiatesthe`vga_controller`module,whilealsoprovidingtheRGBcolorvalues fortheVGAoutput.The`vga_controller`moduleimplementstheVGAtimingandgeneratesthenecessarysynchronization signals.BlockdiagramisshowninFig-3.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 11 Issue: 04 | Apr 2024 www.irjet.net p-ISSN: 2395-0072

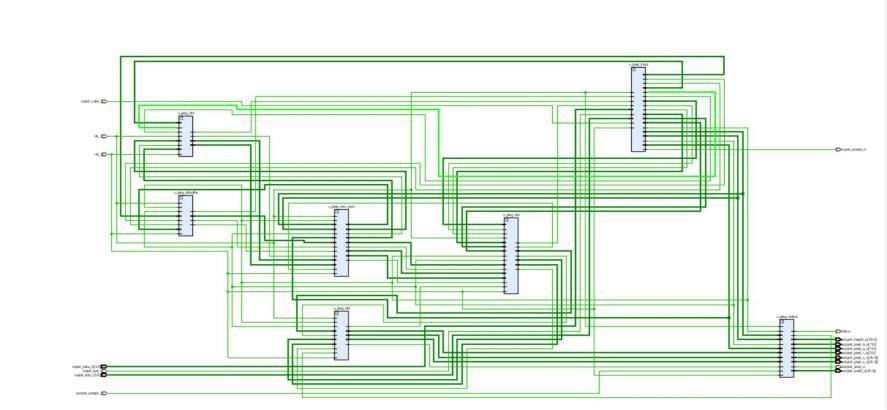

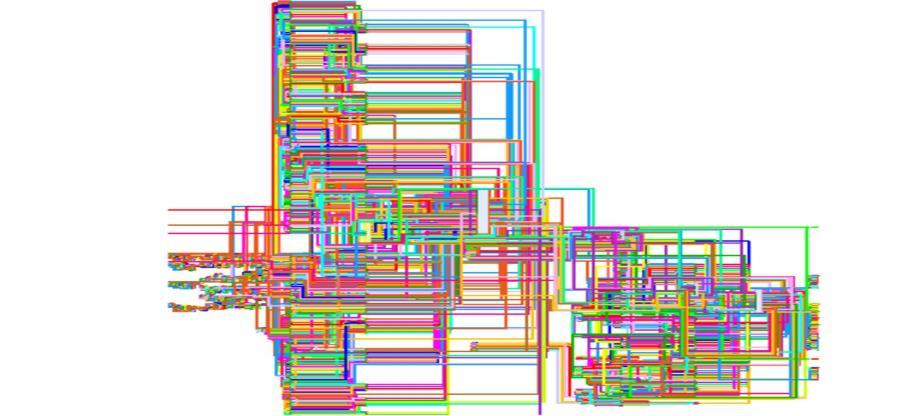

3.1 RTL Schematic of the Proposed Block Diagram

-4:RTLschematicoftheproposedblockdiagram

3.2 Synthesis Result of Decoder Block

InthissectionSynthesisoutputofProposedDecoderBlockisshowninFig5.Inthenextsectiondetailsregardingutilization summaryisexplained

3.3 Utilization summary of Decoder Block

TheUtilization Summaryoffersa concise overview ofhowFPGA resourcesareallocatedwithin the Decoderdesign.This sectionprovideskeyinsightsintotheefficiencyanddistributionofresourcesacrossvariouscomponents.Thisisrepresentedin Table-1.

Table -1: ResourceUtilizationTableofDecoderBlock

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 11 Issue: 04 | Apr 2024 www.irjet.net p-ISSN: 2395-0072

TheUtilizationSummaryoffersaconciseoverviewofhowFPGAresourcesareallocatedwithintheVGAControllerdesign.This sectionprovideskeyinsightsintotheefficiencyanddistributionofresourcesacrossvariouscomponents.Thisisrepresentedin Table-2.

Table -2: ResourceUtilizationTableofVGAController

Inconclusion,theFPGAdesignhasachievedsignificantimprovementsinresourceutilization,showcasingenhancedefficiency acrossvariousparametersasshowninTable-1.TheoptimizedutilizationofSliceLUTsandSliceRegistersreflectsamore judicioususeoflogicelementsSliceLUTs(26.65%)andSliceRegisters(8.06%),contributingtoastreamlinedandpowerful logicimplementationcomparedwith[2]higherSliceLUTutilization(33.26%)andslightlyincreasedSliceRegisterusage (8.44%).TheefficientmanagementofDSPresourcesunderscoresthedesign'scomputationalcapabilities,particularlyindigital signalprocessingapplications.

TheIOsubsystem,althoughexhibitingpotentialforoptimization,requirescontinuedrefinementforseamlessinterfacingand reducedconstraints.Theclockingarchitecture,withitscurrentstability,maybenefitfromongoingresearchintoadaptive strategiesforenhanced,precisionandsynchronization.

Overall,incomparisontoresultspresentedin[2],thecurrentdesigndevelopedismoreoptimizedandefficientdemonstrating effectivemanagementofon-chipmemoryresources.

[1] JunmingShan,DuyaoWang,EryanYang,“HighPerformanceJPEGDecoderBasedonFPGA,” IEEE, 2011.

[2] David J. Lucking, Eric J. Balster Kerry, L. Hill Frank, A. Scarpino, “FPGA Implementation of the JPEG 2000 binary architecture(MQ)decoder,” Springer 2011.

[3] RushikeshTade,SaniyaAnsari,“AccelerationofJPEGDecodingProcessusingCUDA,”InternationalJournalofComputer Applications,Volume120No.9,June2015.

[4] TiagoRodrigues,MarioVestias,“UsingDynamicReconfigurationtoReducetheAreaofaJPEGDecoderonFPGA,” IEEE, 2015.

[5] G.Kyrtsakas,R.Muscedere“AnFPGAImplementationofaCustomJPEGImageDecoderSoCModule,” IEEE,2017.

[6] Dr. Kamlesh Kumar Singh, Dr. Deependra Pandey, “Implementation of DCT and IDCT Based Image Compression and DecompressiononFPGA,”InternationalConferenceonInventiveSystemsandControl ICISC, 2017.

[7] YousefBaroud,JoseManue,MarinosVelarde,ZheWang,SteffenKie,SeyyedMahdiNajmabadi,JajnabalkyaGuhathakurta, SvenSimon,“Architectureforparallelmarker-freevariablelengthstreamsdecoding,” Springer,2017.

[8] S.D.Jayavathi,A.Shenbagavalli,“FPGA-basedAuxiliaryMinutestMQ-CoderArchitectureofJPEG2000,” Springer, 2017.

[9] AnefficientFPGA-baseddynamicpartialreconfigurationdesignflowandenvironmentforimageandsignalprocessingIP cores.

[10] https://digilent.com/reference/programmable-logic/basys-3/reference-manual