MenciÓn de HOnOR

TRABAJO de GRAdO

FACULTAD

CONSIDERACIÓN A SU ALTÍSIMA CALIDAD ACADÉMICA,

MENCIÓN

Módulos

HONOR

TRABAJO DE GRADO TITULADO

Depurador

ce sadores

REALIZADO POR EL ESTUDIANTE

Burgos Martíne

DE LA CARRERA DE INGENIERÍA ELECTRÓNICA , SEGUNDA PROMOCIÓN

POR

FERNANDO VIVEROS MORENO

JUeGO PinG POnG en VHdL

El juego de Pong el cual fue creado en el año 1958, consiste en dos jugadores, cada uno con una raqueta que se puede mover de arriba abajo, una pelota que navega el campo asi como también rebota en los bordes y cuya velocidad aumenta conforme avanza el juego.

Se implemento el juego Pong en una tarjeta de desarrollo que tiene una FPGA (Altera DE0), se diseña un controlador VGA y asi usar el puerto VGA de la tarjeta para visualizar en una pantalla VGA con una resolución mínima de 640x480.

Por último, se seleccionan los actuadores (Raquetas) para ser usadas por cada jugador asi como también se implementa en la FPGA el hardware necesario para usar estos actuadores. Para la descripción de cada uno de los bloques funcionales del proyecto se usó el lenguaje de descripción de hardware VHDL.

Diagrama en bloques

PROceSAdOR en VHdL

Se desarrollo un procesador multipropósito capaz de realizar operaciones aritméticas básicas de suma y resta entre dos números de entre 1 y 16 bits leídos de una memoria RWM de 1024 posiciones.

Además tiene capacidad de interrumpir el programa debido a una señal externa dada por el usuario, y la posibilidad de moverse entre diferentes posiciones de la memoria para así ejecutar programas de mayor complejidad.

El procesador ejecuta operaciones entre datos leídos desde memoria y almacena los resultados de la operación en la misma. Esta memoria es de lectura y escritura y para seleccionar una posición de memoria se debe usar una dirección de 10bits.

Para la descripción de cada uno de los bloques funcionales del proyecto se usó el lenguaje de descripción de hardware VHDL.

Diagrama en bloques Proyecto Procesador

Proyecto Procesador

MediciÓn de cALidAd de eneRGÍA de Un

SincROniZAdO cOn LA LÍneA cOMeRciAL

Para este proyecto se realiza el diseño e implementación de un inversor sincronizado el cual entre sus aplicaciones están: Fuente de poder ininterrumpida y/o Paneles solares. Como características funcionales de este proyecto se tienen:

• Inversor

Vo = 9 VRMS ± 2%

Fo = 60 Hz ± 5%

Po = 15 W

• Sincronización

• Enganche Fo = 60 Hz ± 5% (57 Hz – 63 Hz)

• Medición de calidad.

• Medición con módulo de adquisición

• Acondicionamiento de entrada de voltaje y corriente.

• Rango dinámico de 80 dB

• Variables a medir Vo (RMS), Io (RMS) y THD para estas.

Teniendo en cuenta el diagrama en bloques presentado, cada uno de los bloques fue diseñado exclusivamente para este proyecto, esto incluye los cálculos necesarios asi como la selección de los componentes adecuados para asi cumplir y satisfacer las características funcionales de este proyecto (Acondicionamiento de la señal, PLL, Inversor DC – AC, VCO)

MediciÓn AnGULAR

Este proyecto presenta la concepción, diseño, implementación y operación de un sistema capaz de medir posición angular por medio de un Synchro/Resolver.

Como características funcionales de este proyecto se tienen:

• Se diseño e implemento un oscilador “puente de wien”, el cual es capaz de oscilar a una frecuencia de 400 Hz, con máxima excursión en su salida.

• Se diseño e implemento un circuito Scott-t, un Multiplicador y un Filtro pasa bajas.

• El circuito Scott-t, es para poder realizar la transformación de 3 señales provenientes del Synchro a dos señales, las cuales son aproximaciones de una onda seno y coseno respectivamente.

• Se implemento un circuito multiplicador, el cual realiza la operación entre las señales seno y coseno provenientes del circuito Scott-t.

• Se diseño e implemento un Filtro pasa bajas a la señal proveniente del circuito multiplicador para obtener un valor DC.

• Se acondiciona la señal proveniente del filtro pasa bajas para que esta pueda ser leída y analizada por un Arduino.

• Se diseño e implemento el código con el cual se determina la posición angular del rotor del Synchro haciendo uso de la señal descrita previamente, este código se realizó en el programa Arduino Software IDE.

cASH TeSTeR

Implementar una solución viable a la problemática que más de 595.288 personas sufren en el país al no poder identificar eficazmente la denominación de las monedas de referencia colombiana.

El diseño se compone de:

• Un sensor (transductor) el cual es una resistencia sensible a la fuerza (FSRFlexiForce A101).

• Circuito de acondicionamiento de señal usando un puente de wheatstone asi como también un amplificador de instrumentación y un filtro pasa bajos.

• La señal proveniente del filtro pasa bajos pasada por un circuito detector de picos el cual se encarga de retardar/ampliar la duración del pico de voltaje

• La señal proveniente del detector de picos es enviada a un comparador para clasificar y crear un voltaje DC.

• El voltaje DC proveniente del comparador ingresa a un VCO el cual producirá una variación en frecuencia.

• La frecuencia proveniente del VCO es usada para producir un sonido con el cual es posible identificar el valor de la moneda.

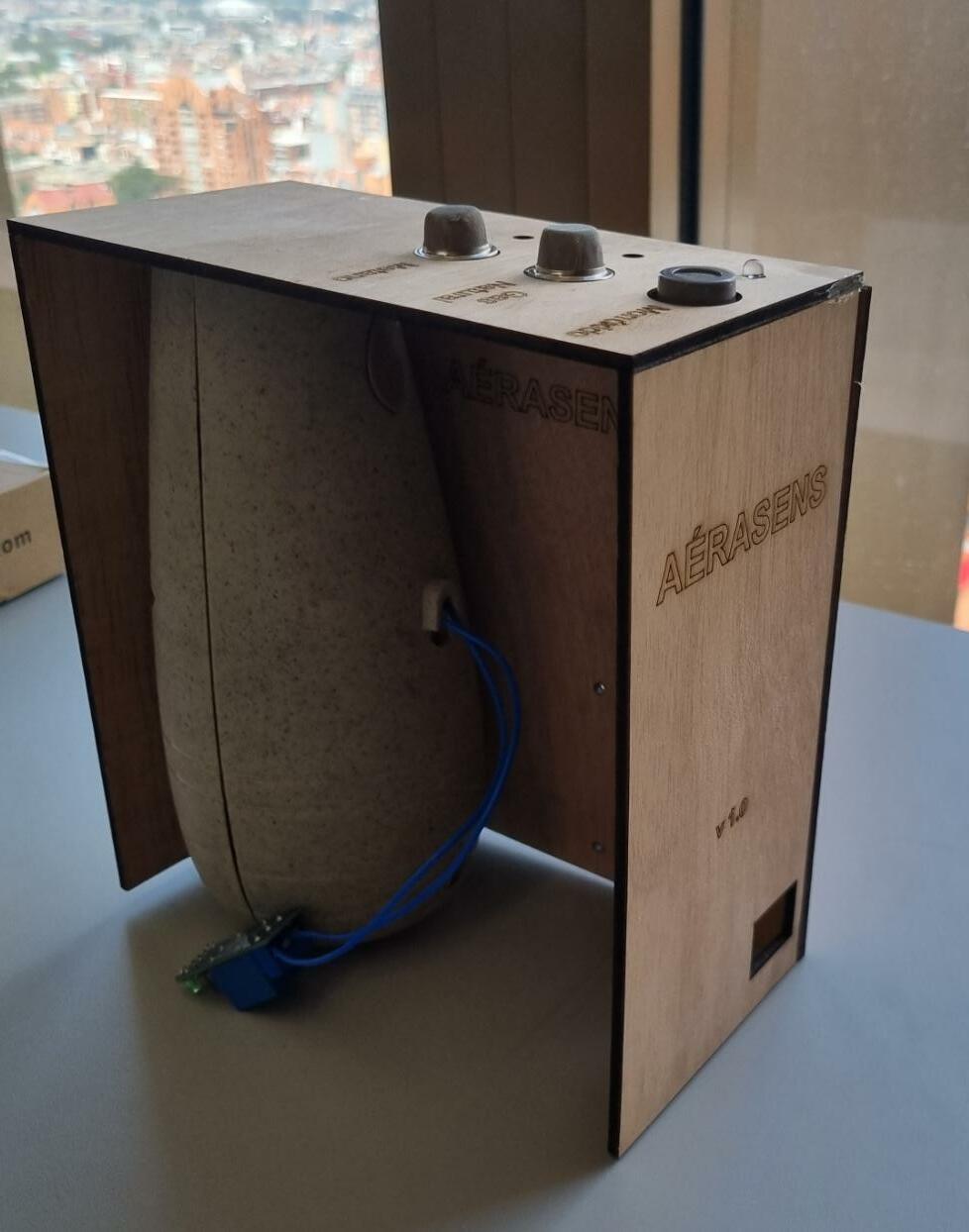

iOT - AMBienTAdOR de AiRe

Este producto está enfocado al área de Domótica, además de ser capaz de aromatizar el ambiente del hogar de manera periódica, este dispositivo puede también salvar vidas.

El usuario podrá visualizar la concentración de gas metano, Gas Natural y Monóxido de Carbono. Este último es un gas inoloro, incoloro y difícilmente detectable sin sensores. Todos altamente peligrosos para el ser humano.

Se presenta un Ambientador Inteligente, con la característica de una página web (como interfaz), el usuario puede interactuar con el dispositivo para monitorear la concentración de Gas Natural y de Gas de Monóxido de Carbono en el ambiente.

En caso de que se detecte alguna concentración de gas alta, se encenderán unos LEDs y comenzará a sonar el Buzzer. Ademas, el usuario podrá ver varias notificaciones de la lectura de gas a su vez que podrá ver el análisis de datos en gráficas.

Circuito del proyecto

Diseño 3D prototipo Implementación del diseño

de

USAndO APRendiZAJe de MAQUinA

Este proyecto está orientado hacia la implementación de algoritmos de aprendizaje de máquina para proponer una solución a un dataset en particular. La base de datos escogida para el desarrollo de este proyecto es Predicciones de Aceptación en Ingeniería (Engineering Placements Prediction), la cual está basada en datos proporcionados por una universidad anónima entre los años 2013 y 2014. Ahora, usando algoritmos de aprendizaje de maquina se determina si un estudiante es aceptado o no en su carrera escogida teniendo en cuenta las características proporcionadas. Partiendo de la premisa anterior el algoritmo a ser implementado es uno de clasificación y supervisado, es decir, se tienen las características y la etiqueta del data set. El algoritmo usado en este proyecto es el de regresión logística

La información fue estructurada siguiendo el modelo CRISP-DM, del cual se plantean las fases de: Business Understanding, Data Understanding, Data Preparation, Modeling y Evaluation, la última fase de despliegue no es tenida en cuenta.

Sección

AnÁLiSiS de AnTenAS TiPO PARcHe AnSYS eLecTROnicS

Diseño y análisis de dos configuraciones de antenas parche, el primer modelo de simulación será una antena parche sin inset, el segundo modelo será una antena parche con inset, ambas con acoplador lambda/4 para mejorar el acople de impedancias.

Se analizan los diferentes parámetros de los dos diseños de antenas como su patrón de radiación, su impedancia real e imaginaria, su parámetro S11 entre otros. Adicionalmente se hace un análisis en cuanto al funcionamiento del inset observando los modos del sustrato, del parche y del acoplador lambda/4.

Posterior al trabajo previo, se procede a seleccionar un paper en el cual se trate el tema de antenas para asi desarrollar un arreglo de antenas parche 1x2 con inset donde se observan y analizan sus parámetros de reflexión y transmisión respecto a los diferentes puertos, acercando más su patrón de radiación cosecante cuadrado requerido y que es obtenido en el paper escogido.

Por último, se realiza el diseño del arreglo de antenas parche 8x2 propuesto en el paper con el objetivo de ver su patrón de radiación de cosecante cuadrado, sus frecuencias de resonancias e impedancias reales e imaginarias en cada frecuencia y directividad y ganancia de la antena.

Para la implementación de un arreglo de antenas parche se tienen las siguientes características de radiación:

• Ancho de banda de 1,93 GHz

• Radiación en la frecuencia X – de 8 a 12 GHz

• Ganancia pico de 14,95 dBi

• Polarización lineal