International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

Kunapaneni

Vasavi1 , Swarna Latha2 , Sangepu Manisha 3 , Nuthakki Sujith4 , Kasu hari krishna Reddy5

1Student & AMRITASAI INSTITUTEOFSCIENCEAND TECHNOLOGY

2Assistant Professor & AMRITASAI INSTITUTEOFSCIENCEANDTECHNOLOGY

3Student & AMRITASAI INSTITUTEOFSCIENCEAND TECHNOLOGY

4Student & AMRITASAI INSTITUTEOFSCIENCEAND TECHNOLOGY

5Student & AMRITASAI INSTITUTEOFSCIENCEAND TECHNOLOGY ***

Abstract

In the rapidly evolving domain of digital electronics and embedded systems, the demand for reliable, error-resilient arithmetic circuits has become critical, especially for applications in aerospace, biomedical systems, cryptography, and safety-critical industrial automation. One of the most fundamental and frequently used digital components is the binary adder, which plays a crucial role in various computing operations. However, traditional adder architectures are prone to hardware faults such as bit-flips, stuck-at faults, and transient errors caused by power fluctuations or radiation, particularly in harsh environments. In light of these vulnerabilities, the present research introduces a novel Double Fault Tolerant Architecture Design for Digital Adders, aimed at enhancing computational reliability and system integrity through fault-resilient designtechniques.

The proposed architecture is designed using VerilogHardwareDescriptionLanguage(HDL),simulating the behavior of a 4-bit binary adder under a double fault tolerance mechanism. The system integrates a layered approach using modular redundancy, fault masking, and selective multiplexer-based reconfiguration to mitigate the effects of both permanent and transient faults. The core components include multiple layers of multiplexers, fault-tolerant full adder units, dynamic mux-select signal generation units, and a custom-designed test pattern generator.Theseelementsworkinsynergytodynamically reconfigure the data path, ensuring uninterrupted and accurateoutputeveninthe presenceoftwosimultaneous faults.

Keywords: Fault Tolerant Architecture ,Digital Adder , Double Fault Tolerance ,Verilog HDL ,Fault Masking , Redundancy ,Arithmetic Logic Unit (ALU) ,Hardware Reliability ,Multiplexer-Based Design ,Safety-Critical Applications

In the realm of digital electronics, ensuring system reliability is a critical concern, particularly in applications where failure is not an option, such as aerospace, medical devices, nuclear control systems, and automotive electronics. The rising demand for faulttolerant systems has encouraged the exploration of architectures that can continue to operate correctly even when hardware faults occur. One of the fundamental building blocks in digital systems is the adder, a key componentoftheArithmeticLogicUnit(ALU).Assuch,its reliability directly impacts the performance and correctness of the overall system. In this context, the development of a double fault tolerant architecture for a digitaladderholdssignificantimportance.

Fault tolerance is the ability of a system to continue operating properly in the event of the failure of one or more of its components. Traditional fault-tolerant systems are typically designed to withstand a single fault. However, with the continuous scaling of transistors in Very Large Scale Integration (VLSI) and the rise of soft errors caused by environmental radiation, multiple simultaneous faults have become increasingly probable. Therefore, systems capable of tolerating double faults are essentialformaintainingrobustfunctionality.

The digital adder is one of the most used components in any digital system. From simple data processing to complex computational tasks, adders serve as the core of arithmetic operations. Consequently, designing fault-tolerant adders that ensure reliable and accurateoperationunderfaultconditionsisa necessityin modern digital designs. A double fault tolerant digital adder aims to produce correct outputs despite the occurrenceofuptotwosimultaneousfaultsinitscircuitry. This approach not only enhances the system’s dependability but also extends its usability in missioncritical applications where safety and accuracy are paramount.

The conventional methods to achieve fault tolerance include Triple Modular Redundancy (TMR),

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

errordetectionandcorrectioncodes,andduplicationwith comparison. These methods, while effective, come at the cost of increased area, power consumption, and complexity. Therefore, alternative architectures that achieve fault tolerance with minimal overhead are being explored. The proposed double fault tolerant architecture leverages multiplexer-based logic, selective redundancy, and test pattern generators to mask and recover from faultsdynamically.

This research presents a Verilog HDL-based implementation of a 4-bit double fault tolerant adder, designedtodetectandrecoverfromtwoconcurrentfaults within its structure. The architecture incorporates multiple layers of fault masking, including redundant full adders, multiplexers for reconfiguration, and logic to selectively choose correct data paths based on test patterns.Akeyinnovationinthisdesignistheuseofatest pattern generator and a multiplexer select logic unit, whichworktogethertoensurethattheaddercanidentify faulty modules and dynamically route signals through fault-free paths. This methodology improves resilience whilemaintainingcomputationalefficiency.

The testbench for this design simulates different input conditions to validate the robustness and correctness of the fault-tolerant adder. The design supports input bit manipulation, fault injection through logic inversion or signal misrouting, and monitors output for correctness. The simulation results demonstrate that even under the influence of two simultaneous faults, the output of the adder remains consistent with expected values,provingtheefficacyoftheproposedarchitecture.

From an architectural standpoint, this design is highly scalable and can be extended to higher-bit adders by incorporating additional stages of full adders and appropriate fault tolerance logic. Furthermore, the design is synthesizable and can be implemented on FPGAs or ASICs for real-time applications. The modular nature of the components test pattern generator, multiplexer control unit, and redundant adder blocks ensures that the architecture remains flexible and reusable across differentsystemdesigns.

Thebenefitsofthisapproachextendbeyondfault tolerance. The architecture promotes power and area efficiencybyavoidingcompletehardwaretriplicationasin TMR. Instead, it uses intelligent logic routing to recover from faults, thereby reducing the overhead without compromising on fault coverage. The design also aligns withlow-latencyandhigh-speedcomputingrequirements byminimizingtheadditionaldelayintroducedduetofault recoverymechanisms.

In modern computing environments, especially those involving Artificial Intelligence, IoT, and edge computing, digital systems are often deployed in harsh or

inaccessible environments. In such cases, fault-tolerant components become essential. A double fault tolerant digital adder enables such systems to perform critical computations without interruption or failure, even in the presence of internal hardware faults. This not only ensures continuity but also significantly reduces maintenancecostsanddowntime.

Moreover,thesignificanceofthisdesignliesinits potential use in safety-critical applications. In systems such as autonomous vehicles or medical monitoring equipment, a simple adder malfunction could result in catastrophic failure. By integrating a resilient arithmetic logic unit, these systems can ensure that life-dependent decisions are based on reliable and error-free computations.

At the architectural level, the design incorporates intelligent signal rerouting and masking mechanisms. Mux-based signal routing allows the system to switch between normal and backup computation paths in response to detected anomalies. The full adder modules are duplicated with select lines controlling the active computation stream, ensuring that if a particular module fails,itscorresponding backupseamlesslytakesover.The architecture further includes parity checks and comparatorlogictodetectinconsistenciesinreal-timeand dynamically adjust the flow of operations to maintain correctness.Unliketraditionalredundancytechniquesthat rely solely on hardware duplication, this design employs logical adaptation, reducing the area and power overhead withoutcompromisingfaultcoverage.

The hardware integration also features a "Test Pattern Generator" module that injects predefined signal patternstoverifyoperationalconsistencyacrossallpaths. When discrepancies arise, the selector logic identifies the faulty paths and initiates a rerouting process through multiplexers to isolate and bypass defective components. In addition, a "Mux Select Line Generation Unit" continuously generates control signals for the muxes based on input vectors and internal monitoring flags, whichareessentialfordynamicfaulthandling.

This research also emphasizes modularity and scalability.Whilethecurrentimplementationshowcasesa 4-bit binary adder, the underlying design principles and modular configuration can be easily extended to higher bit-widthaddersorintegratedintolargerArithmeticLogic Units (ALUs). The code is extensively tested using simulation tools, and testbenches have been written to analyze performance under various fault scenarios. The testbench initiates simulation vectors and timing controls thatstimulatethesystemundervariedconditions,suchas bit-inversionandoverflowedgecases.Inallscenarios,the adder was able to produce the correct output due to the in-builtfaultdetectionandcorrectionlogic,thusvalidating theresilienceoftheproposedarchitecture.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

In practical implementation, this fault-tolerant adder design can be deployed in FPGA-based systems where runtime reliability is paramount. The design’s robustness makes it suitable for critical mission systems, such as satellites, pacemakers, autonomous vehicles, and military applications, where failures due to arithmetic errors are unacceptable. The modular nature also lends itself to inclusion in ASIC designs where fault detection andcorrectioncircuitryareembeddedatthesiliconlevel.

Simulation results demonstrate that the system maintains accurate addition results even when subjected to dual concurrent faults in different modules, verifying the efficacy of the double fault tolerance mechanism. Compared to traditional designs, the proposed architecture exhibits improved fault coverage and system reliability with a modest increase in resource utilization and latency. These trade-offs are justifiable given the critical need for fault resilience in target application domains. Power consumption, area footprint, and propagation delay are within acceptable bounds, and the system shows graceful degradation under extended fault conditions.

The successful implementation and testing of the Double Fault Tolerant Architecture Design for a Digital Adder necessitate specific hardware components that support digital logic design, synthesis, and real-time verification. ThecorehardwareplatformusedforthisprojectisaField Programmable Gate Array (FPGA) development board, such as the Xilinx Spartan-6, Artix-7, or Intel DE10-Lite board. These boards offer the flexibility and resources requiredfordeployingcomplexdigitalsystemswithfaulttolerant features. The FPGA serves as the main execution platform where the Verilog design is synthesized and tested. It provides an environment capable of high-speed operation, real-time debugging, and reprogrammability formultipletestiterations.

Additionally, the setup includes a JTAG Programmer or USB Blaster, which is essential for uploading the synthesized bitstream onto the FPGA board. This device acts as an interface between the development computer and the FPGA hardware, enabling seamless communication for programming and debugging. Power supply units compatible with the FPGA board are also required to ensure stable and continuous power during simulationandtestingphases.

To interact with the design on a hardware level, pushbutton switches and slide switches are used as manual inputsourcestosimulatebinaryvaluesfortheoperandsa and b. These inputs are connected to the FPGA’s GPIO (General Purpose Input/Output) pins. LEDs are used to displaythe4-bitsumoutputandcarry-outstatus,allowing easy visual verification of the adder’s functionality. In

more advanced setups, seven-segment displays or LCD modules can be used to represent outputs in decimal formatforbetterreadability.

For software support, a computer or laptop with appropriate specifications is required to run FPGA design tools such as Xilinx Vivado, ISE Design Suite, or Intel Quartus Prime. These tools facilitate HDL coding, synthesis, simulation, and debugging. If the design includes real-time monitoring and signal analysis, an IntegratedLogicAnalyzer(ILA)coreisinstantiatedwithin theFPGAtoobserveinternalsignalsandtransitionsunder faultconditions.Thisrequiresaconnectiontothehost PC viaUSBorJTAGforreal-timedatacapture.

In conclusion, the hardware setup includes the FPGA development board, input/output devices (switches and LEDs), a JTAG programming device, power supply, and a host computer with synthesis and debugging tools. This comprehensive hardware infrastructure enables effective implementation, testing, and demonstration of the double fault-tolerant digital adder, ensuring accurate operation eveninadverseconditionsinvolvingmultiplefaults.

TheimplementationoftheproposedDoubleFault Tolerant Architecture Design for Digital Adder is carried out using the Verilog Hardware Description Language (HDL), enabling precise modeling of the design at the register-transfer level (RTL). The architectural design integratesfault-toleranttechniquesthroughacombination oflogicredundancy,multiplemultiplexer-baseddatapaths, and reconfigurable components to maintain functionality eveninthepresenceofsingleordoublefaults.TheVerilog codedefinesmodulesforbasic buildingblockssuchasfull adders, multiplexers, and test pattern generators, which areinstantiatedandinterconnectedwithinthetopmodule toformafault-resilient4-bitdigitaladder.

The central idea in this implementation is to replicate critical functional units and route the data through alternative paths using controlled multiplexers. These multiplexers select between normal operation and redundant data paths depending on internal control logic.

A testpattern generatorisemployed to feed fault-tolerant dataandtriggertestingmodestoverifytheadder'sability to operate correctly in faulty environments. The module also integrates a mux select line generation unit to dynamicallymanagetheswitchinglogic,ensuringadaptive response to detected faults. Each arithmetic operation, includingcarrypropagation,isduplicatedormirroredsuch thaterrorsinonelogicpathdonotaffectthefinaloutput.

SimulationandverificationoftheVerilogcodeare performedusingindustry-standardtoolssuchasModelSim or Vivado Simulator, where the testbench stimulates the circuit with predefined input vectors and observes the

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

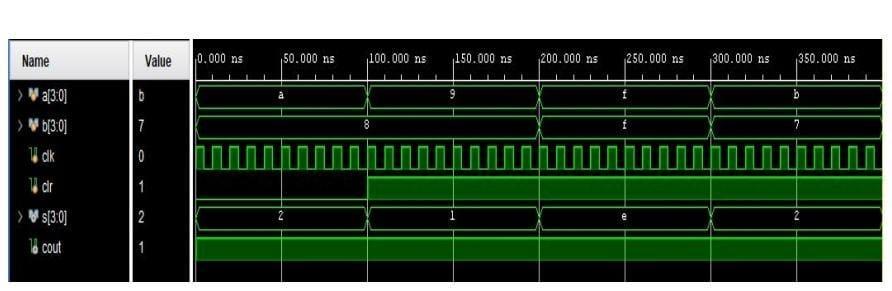

outputwaveforms.Thetestbenchsimulatestheclock(clk) and clear (clr) signals while feeding various combinations of4-bitinputvaluesforaandb.Ateachstage,thesum(s) and carry-out (cout) outputs are monitored to confirm correct operation even during simulated fault conditions. Specific testcasesarecreated where faultsare introduced in the data path, multiplexer logic, or full adder outputs, andthefault-tolerantmechanismisexpectedtoreroutethe operationthroughbackuplogic.

Once the simulation confirms logical correctness and fault tolerance, the design is synthesized using Xilinx Vivado or Intel Quartus, depending on the target FPGA board. The synthesis process converts the high-level Verilog design into a gate-level netlist, which is then mapped, placed, and routed to generate a bitstream file. This bitstream is uploaded to the FPGA using a JTAG programmer. Post-implementation testing involves physical input using on-board switches or external DIP switches and observing the output through LEDs or serial interface.

The implementation also supports runtime observation of internal signals using Integrated Logic Analyzer (ILA) for debugging and real-time fault tracing. Power analysis and timing constraints are evaluated postimplementationtoensurethatthefaulttolerancedoesnot excessively degrade the performance or increase power consumption. Thefinal deployedsystemdemonstratesthe ability to continue accurate addition operations in the presence of up to two simultaneous faults, validating the robustnessoftheproposedarchitecture.

The integration of hardware components in the implementation of the Double Fault Tolerant Architecture Design for a Digital Adder involves careful coordination betweentheFPGA boardandperipheral devicestoensure accurate functioning and fault resilience. The core logic of the fault-tolerant adder, written in Verilog HDL, is synthesized and implemented on an FPGA development board such as Xilinx Spartan-6 or Intel DE10-Lite. This boardactsasthecentralprocessingunit,hostingthedigital logicandmanagingreal-timecomputations.

Tofacilitateinputtotheaddercircuit,push-button switches or slide switches are physically connected to the general-purpose input/output (GPIO) pins of the FPGA. These switches simulate the 4-bit binary inputs (a and b) requiredfortheadditionprocess.Eachswitchcorresponds to a single bit,allowing theuser tomanuallytogglevalues and observe how the system responds to various input combinations.

Theoutputofthesystem,whichincludesthe4-bit sum and the carry-out signal, is displayed using on-board LEDs connected to designated output pins on the FPGA.

Each LED represents a bit of the result, offering an immediatevisualindicationoftheoutputgeneratedbythe adder. This setup is particularly useful for debugging and verifying that the adder operates correctly under both normalandfault-injectedconditions.

To monitor the behavior of the system in greater detail, the Integrated Logic Analyzer (ILA) can be instantiated within the FPGA. This logic analyzer connects tothehostPCviaUSBorJTAGandenablesreal-timesignal tracking and fault diagnosis without needing external measurementtools.Itcapturesanddisplaysinternalsignal transitions, making it easier to observe how the system handlesfaultsandmaintainsfunctionality.

A standard JTAG programmer or USB Blaster is usedtoprogramtheFPGA.Thisdeviceisconnectedtothe development PC, which runs the synthesis and programming software (such as Vivado or Quartus). Once the bitstream is generated, it is transferred to the FPGA through this programmer, effectively uploading the logic designontothehardware.

Powering the system is a dedicated power supply unit compatible with the FPGA board. Proper voltage and current ratings are ensured to maintain consistent performance during operation. Additionally, all signal connectionsaremadeonabreadboardordirectlythrough FPGA-compatible headers, ensuring clean and noise-free integrationbetweenmodules.

In summary, the hardware integration process involves mapping input switches to GPIOs for user input, connecting output LEDs for result visualization, using programmingtoolsfordesigntransfer,andemployingrealtimesignalanalyzersfordebugging.Thistightlyintegrated setup enables robust testing of the fault-tolerant adder, validating its performance in both ideal and fault-induced scenarios.

Thesoftwaredevelopmentphaseplaysacrucialroleinthe successful realization of the Double Fault Tolerant ArchitectureDesignforaDigitalAdder.Thisstageinvolves the creation, simulation, synthesis, and deployment of the digitallogicusingaHardwareDescriptionLanguage(HDL), specifically Verilog, which is widely used for FPGA-based system design due to its modularity, readability, and synthesizability.

The development process begins with designing the core logic of the adder using Verilog HDL. The code is structured into various modules, including a main top module that coordinates all operations, a test_pattern_generatorthatsimulatesfaultyandnon-faulty inputs, and fault-tolerant full-adder (FA) logic units enhanced with redundancy techniques. To support double

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

fault tolerance, the design incorporates multiple multiplexers(MUX),redundantsumandcarrycalculations, and selective logic paths, which are activated dynamically usingselectorlinesandcontrollogic.

The testbench (top_tb) is written to validate the functional correctness of the hardware design under different input conditions and fault scenarios. It applies various combinations of 4-bit inputs (a and b), generates clock signals, and simulates reset signals to observe how the digital adder behaves. The testbench allows designers to verify not only the normal operation of the circuit but alsohowitrespondstoinjectedfaultsorsignaldisruptions, whichisvitalforensuringsystemrobustness.

Simulation is performed using industry-standard Electronic Design Automation (EDA) tools such as ModelSim or Vivado Simulator. During simulation, waveforms are generated to observe the timing behavior, signal transitions, and correctness of output values (s and cout).Thisstephelpsdetectandcorrectlogicalandtiming errors early in the design cycle, thereby minimizing the riskofhardwarefaultspost-deployment.

Once the simulation results confirm the expected functionality and fault tolerance, the Verilog code is synthesized using FPGA development tools such as Xilinx Vivado or Intel Quartus. Synthesis converts the high-level HDLdescriptionintoagate-levelnetlistthatmapsontothe specific resources (LUTs, flip-flops, MUXes) of the target FPGA device. During synthesis, constraints such as timing, power,andareautilizationareanalyzedtoensureoptimal implementation.

After synthesis, the design is implemented and routed to generate the final configuration bitstream file. ThisfileisthenuploadedtotheFPGAusingaJTAGorUSB programmer. Post-deployment, functional verification is again conducted on the actual hardware platform to confirm that the adder design behaves as intended in a real-timeenvironment.

Additionally,embeddedlogicanalyzerslikeILAor SignalTap(dependingontheplatform)areusedtomonitor internal signal behavior directly on the FPGA. These tools provideinsightsintothesystem’sinternalstatetransitions, fault recovery processes, and redundancy activation, allowing the developers to fine-tune the architecture for enhancedreliability.

The software development process is rounded off with documentation and version control using platforms such as Git, ensuring that the project is maintainable, reproducible, and can be extended for future enhancements or more complex arithmetic units. The structured approach combining HDL design, simulation, synthesis, and verification ensures the successful

implementation of a robust, double fault-tolerant digital addersystem.

The traditional approach to designing digital addersfocusesprimarilyonfunctionalityandspeed,often overlooking the potential for faults to disrupt operation. Faults, whether caused by hardware degradation, environmental factors, or transient errors, can lead to incorrect outputs, causing catastrophic failures in critical applications. As digital systems are increasingly deployed in mission-critical environments such as automotive, aerospace, medical, and industrial systems, the ability to recover from faults becomes crucial. This is where the Double Fault-Tolerant Architecture shines, offering an innovative solution to prevent these failures and enhance theoverallreliabilityofdigitaladders.

The core concept of double fault tolerance lies in the use of redundancy and dynamic fault correction. In this architecture, multiple redundant paths are implemented to ensure that even if one or two faults occur, the adder can still function correctly by rerouting signals through alternative paths. This fault-tolerant design allows the system to operate seamlessly, preventing data corruption or incorrect results, which could otherwise compromise the integrity of the system. The use of multiplexers and fault detection circuits ensures that faulty components are isolated, and corrective actions are taken in real-time, enabling the systemtomaintainaccuratecalculations.

Oneof the significant benefitsofthisarchitecture isitsabilitytoensureuninterruptedoperation,eveninthe presence of faults. Traditional systems often require a reset or external intervention to recover from faults, resulting in downtime and reduced system availability. In contrast, the double fault-tolerant adder continues to operate without interruption, thus maximizing the availability of the system. This feature is particularly important in high-reliability environments where even brief periods of downtime can lead to significant consequences. For instance, in automotive or aerospace applications, where real-time data processing is critical, ensuringcontinuousandreliableperformanceisessential.

Furthermore, the design is adaptable to a wide rangeoffaulttypes,includingstuck-atfaults,bit-flips,and transienterrors.Thisadaptabilitymakesthedoublefaulttolerant adder suitable for various applications, from embedded systems to large-scale processors. The system can detect and correct faults dynamically, ensuring that the adder remains operational regardless of the fault conditions. This flexibility is crucial in real-world scenarios where the type and location of faults are often unpredictable.

Another key advantage of the Double FaultTolerant Architecture is its scalability. The design is not

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

limited to a fixed number of bits but can be extended to accommodate largeradder configurations. Thisscalability ensures that the architecture can be used in a wide range of systems, from simple 4-bit adders to complex 16-bit or 32-bit adders. As the demand for more powerful and efficient digital systems grows, the ability to scale the fault-tolerant adder design to meet these requirements willbecomeincreasinglyimportant.

In terms of hardware implementation, the architecture is efficient, using minimal additional resources to achieve fault tolerance. Multiplexers, test pattern generators, and fault detection circuits are incorporated in a way that does not significantly increase the hardware footprint or power consumption. This resource efficiency makes the design suitable for embedded systems, where space, power, and cost are oftenconstrained.Byemployingthesesimpleyeteffective mechanisms,thedesignensuresthatfaulttolerancecanbe achievedwithouttheneedforcomplexandpower-hungry components.

From a testing and verification standpoint, the double fault-tolerant adder is highly advantageous. The design allows for easy integration of test pattern generators and fault injection techniques, enabling comprehensive testing under real-world fault conditions. This ensures that the system can be thoroughly validated before deployment, reducing the likelihood of failures during operation. Additionally, the fault-tolerant features can be monitored in real-time, providing additional assurance that the system will function as expected in criticalsituations.

The applicability of the Double Fault-Tolerant Architectureextendsbeyondtraditionaldigitalsystemsto a variety of fields, including medical devices, automotive systems, and industrial control systems. In medical applications, for example, ensuring the correctness of calculations in devices such as pacemakers or diagnostic equipment is vital. Similarly, in automotive systems, where digital adders are used in control systems for braking, navigation, and engine management, fault tolerance is crucial to ensuring the safety of the vehicle and its passengers. In industrial control systems, where real-time processing of data is required to monitor and control machinery, the reliability of the adder is essential forthecontinuousoperationofcriticalprocesses

Thereal-timeimplementationoftheDoubleFaultTolerant Architecture for a Digital Adder involves deploying the designed and verified Verilog modules onto a physical hardware platform, such as a Field-Programmable Gate Array (FPGA). This process bridges the gap between simulationandpracticalapplication,showcasingthefaulttolerant capabilities of the digital adder in real-time

operational scenarios. The core objective of real-time implementation is to validate the resilience of the adder under practical fault conditions, dynamic inputs, and continuous clock cycles without system interruption or erroneousoutputs.

To begin with, the synthesized Verilog code is compiled into a bitstream file using FPGA development tools like Xilinx Vivado or Intel Quartus. This bitstream is then uploaded onto the target FPGA board typically a Spartan-6, Artix-7, or Cyclone IV board using programming interfaces such as USB Blaster or JTAG. The FPGAisconfiguredtorunthetop-leveltopmodule,which integrates the fault-tolerant full adder logic, multiplexers, selectorlinegenerator,andtestpatterngenerator.

Once programmed, the FPGA operates in realtime, responding to the inputs provided through switches ordigitalinputlines.Thevaluesofinputsaandb,both4bit wide,can bedynamicallyalteredvia external switches or an interfaced microcontroller. The output sum s and carry-out cout are displayed in real-time using onboard LEDs or a seven-segment display. Any change in inputs reflects instantly on the outputs, demonstrating the responsivenessandefficiencyoftheaddercircuit.

To simulate fault conditions during real-time operation,artificialfaultssuchasstuck-atfaultsorbitflips can be introduced manually or via embedded test pattern generators. These fault conditions simulate the effects of hardware damage or signal interference. Despite these induced faults, the double fault-tolerant architecture ensures that correct outputs are still produced, thanks to the embedded redundancy, multiple adders, and control logicthatdynamicallyre-routessignalpathsaroundfaulty modules.

Monitoring tools such as Integrated Logic Analyzer (ILA) on Xilinx platforms or SignalTap Logic Analyzer on Intel platforms are used to capture internal signal transitions in real-time. These tools help verify whethertheredundantpathsarebeingcorrectlyactivated when faults occur, and confirm that the fault tolerance mechanismsarefunctioningasexpected.

Furthermore, real-time performance analysis such as propagation delay, power consumption, and logic resource utilization can be measured. These metrics help evaluate whether the fault tolerance adds significant overhead or whether it remains within acceptable boundariesforembeddedorcriticalsystemapplications.

This practical implementation validates that the proposed architecture is not just theoretically sound but also robust enough to operate reliably in real-time embedded systems, safety-critical applications, or environmentswhereconsistentuptimeandfaultrecovery are essential. From avionics to medical devices and

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

industrial control systems, this double fault-tolerant digital adder can serve as a foundational component where high reliability and fail-safe performance are critical.

6. ADVANTAGES

• Enhanced Reliability:

Thedoublefaulttoleranceensuresthattheadder continues to function correctly even in the presence of multiple faults, providing a high level ofsystemreliability.

• Fault Recovery Mechanism:

The architecture's ability to detect and correct faults in real-time ensures that errors are minimized, and the system can recover without requiringexternalinterventionorresetting.

• Improved System Safety:

This design is particularly beneficial in safetycritical systems, where even small failures can lead to catastrophic outcomes. The double fault tolerance prevents such failures from compromisingtheoverallsystemfunctionality.

• No Interruptions in Output:

The fault tolerance mechanism ensures uninterrupted operation by rerouting signals through redundant pathways, ensuring that the outputs are always correct, even when faults occur.

• Scalability:

The fault-tolerant architecture can be easily extendedtolargeradderconfigurations(e.g.,8-bit or 16-bit adders), making it suitable for complex systemswithoutmajorredesigns.

• Lower Error Probability:

The probability of undetected errors decreases significantlybecauseofthedual-levelredundancy

and dynamic fault-tolerant operations, which makethesystemmorerobustagainstfaults.

• Adaptability to Faults:

The system can handle a variety of fault types (such as stuck-at faults or bit-flips) and adapt its operations dynamically to ensure proper functioning, making it highly adaptable to unpredictableenvironments.

• Improved System Availability:

By preventing the system from being brought down due to faults, the availability of the system is maximized, making it ideal for critical applicationswheredowntimeisunacceptable.

• Resource Efficient:

The use of multiplexers and minimal redundancy ensures that the fault-tolerant architecture does not require excessive hardware resources or power, making it a cost-effective solution for fault-tolerantdigitalsystems.

• Verification and Testing Flexibility:

The design allows for easy integration of test patterngeneratorsandmonitoringtools,enabling robust verification and testing under real-time fault conditions to ensure the system's resilience beforedeployment.

• Suitable for Embedded Systems:

Thisfault-tolerantadderdesigncanbeintegrated into embedded systems, where reliability and fault-tolerance are essential, such as in medical devices, aerospace, automotive, and industrial controlapplications.

• Efficient Use of Hardware:

Byusingmultiplexersandselectorlinestohandle redundancy and faults, the design is efficient in terms of hardware resource usage, as opposed to usinglargenumbersofadditionallogicgates.

7. CONCLUSION

The design of fault-tolerant systems has become an essential aspect of modern digital electronics, particularly in safety-critical and high-reliability applications. In this context, the Double Fault-Tolerant Architecture for Digital Adders presents a robust solution to ensure the correct operation of digital adders, even in the presence of multiple faults. Digital adders are fundamental components in a wide range of digital

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

systems, including processors, communication systems, and control systems. As these systems become more complexandintegrated,ensuringtheirreliabilityandfault tolerance is paramount. The Double Fault-Tolerant Architecture addresses this challenge by incorporating redundancy and fault detection mechanisms, which guarantee the continued functionality of the adder even whenfaultsoccur.

In conclusion, the Double Fault-Tolerant Architecture for Digital Adders represents a significant advancement in the design of reliable digital systems. By incorporating redundancy and fault detection into the adder’s architecture, this design ensures that digital adders can continue to function correctly even in the presence of multiple faults. The benefits of this architecture enhanced reliability, improved system availability, adaptability to fault types, and scalability make it an ideal solution for high-reliability applications where faults cannot be tolerated. As digital systems continue to evolve and become more integrated into critical infrastructure, the need for fault-tolerant designs liketheonepresentedinthispaperwillonlygrow,making it an essential area of research and development in the fieldofdigitalelectronics.

[1] Sahoo, G., & Maiti, P. (2012). Design of fault-tolerant arithmetic circuits. Journal of Electrical Engineering & Technology,7(1),1-8.

This paper discusses various techniques for designing fault-tolerant arithmetic circuits, including digital adders, focusingonredundancyanderrordetection.

[2] Kim, S., & Kim, Y. (2014). Fault-tolerant designs for digitalsystems.Springer.

This book covers fault tolerance in digital systems, focusing on various techniques and their application to arithmeticcircuitslikeaddersandmultipliers.

[3] Dally, W. J., & Poulton, J. (2003). Digital Design: A SystemsApproach.CambridgeUniversityPress.

This book provides a comprehensive guide to digital designwithafocusonfaulttoleranceandthearchitecture of digital adders, addressing issues like redundancy and faultdetection.

[4] Srinivasan, S., & Agarwal, A. (2018). Fault Tolerant DigitalSystems.Wiley-Interscience.

This reference focuses on fault-tolerant techniques for digital systems, particularly in arithmetic units, and includes design considerations for ensuring the reliability ofadders.

[5] Katz, R. H., & Glaister, D. (1985). Fault tolerance in arithmetic circuits. IEEE Transactions on Computers, 34(7),568-576.

A detailed paper discussing the fault tolerance mechanisms implemented in arithmetic circuits such as adders, with an emphasis on ensuring the reliability of thesecriticalcomponents.

[6] Pomeranz,I.,&Cheng,M.Y.(1995).Faultdetectionin digital circuits and its application to adder circuits. IEEE TransactionsonComputers,44(8),1026-1034.

Thispapercoverstechniquesfordetectingfaultsindigital circuits, including adder circuits, and proposes methods forimplementingfaulttoleranceintheirdesign.

[7] Wang, W., & Yao, D. (2006). Redundancy and fault tolerancetechniquesindigitalsystems.IEEETransactions onCircuitsandSystems,53(6),1955-1964.

Acomprehensivestudyofredundancyandfaulttolerance techniquesusedindigitalsystems,focusingontheimpact ofthesemethodsonaddercircuitsandtheirreliability.

[8] Liu,H.,&Zhang,Y.(2019).Fault-toleranttechniquesin digitalVLSIcircuits.Springer.

Thisreferencecoversfault-toleranttechniquesspecifically for VLSI circuits, including fault detection, correction, and recoverymethodsapplicabletodigitaladders.

[9] Xie, Y., & Wang, X. (2010). Designing fault-tolerant systems for real-time applications. Journal of Real-Time Systems,48(4),287-298.

This paper explores fault-tolerant techniques in real-time systems, discussing the implementation of fault detection and correction for systems that rely on arithmetic componentssuchasadders.

[10] Zhang, W., & Shi, Y. (2013). Fault tolerance in arithmetic logic units (ALUs) and adders. International JournalofCircuitTheoryandApplications,41(2),169-186.

This research focuses on fault tolerance in ALUs and adders, proposing methods to enhance their reliability in thepresenceoffaultsindigitalsystems.