International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

Shishir Bagal1 , Atharva Jangade2 , Ishwita Nagrikar3 , Anjali Sonwane4 , Mrunal Katre5 , Pranay Dhopekar6

1Assistant professor, Dept of Electronics and Telecommunication, KDK College of Engineering, Maharshtra, India 23456UG student, Dept of Electronics and Telecommunication, KDK College of Engineering, Mahrashtra, India

Abstract - Quantum-dot Cellular Automata (QCA)isthenew area of nanotechnology that gives an alternative paradigm of designing digital-circuitry thus it could replace the existing technologies, like CMOS and FinFET. Traditional semiconductor systems are faced with mounting problems, such as high-power dissipation,strongshort-circuiteffectsand a lack of smaller size scaling. QCA is a better solution because of its high speed, low power consumption and capability of high density. QCA is an implementer of logical functions based on the spatial arrangement of electrons trapped in quantum dots instead of current flow, potentially a contender in nanoscale computing in the future. Thecurrentpaperassesses various studies related to design and synthesis of Universal Shift Registers (USR) being executed by QCA Designer tool. USRs are essential parts of digital systems which give a mechanism of data storage, transfer and control. This paper has reviewed several differentUSRarchitecturesbasedonQCA and has explored ways of improving their performance in terms of power consumption, runtime speed,andphysicalsize. In addition, it compares QCA implementations with those similar designs based on CMOS and FinFET technology to identify the different benefits and restrictions of these technologies. Progressing findings show that QCA designs are faster, more energy efficient; however, they still face the pitfalls of fabrication related inefficiencies, complexities in clock distribution as well as noise susceptibility. It ends the study with both research directions to be further pursued by the application of potential solutions, and hypothesizes that with a further development of the methods of fabrication and testing, QCA could become a practical architecture of future nanoelectronics circuitry.

Key Words: CMOS, FinFET, QCA, Nanotechnology, Quantum Physics

1.INTRODUCTION

Constant scaling of the complementary metal-oxidesemiconductor(CMOS)technologyhascomeclosetoapoint whereitisincreasinglybecomingimpossibletoreducethe sizeofthedevice.Leakagecurrent,short-circuiteffects,high power density and reduced reliability of the devices presentlypresentastrenuousconstraintonincreasedCMOS andFinFETdevicesperformance.Asaresult,thereexistsa growing empirical research on the development of alternativenanotechnologiesthatcanoverlayphysicaland operational limits of traditional transistor based

architectures. An alternative is Quantum -Dot Cellular Automata(QCA).UnlikeCMOS,whichusescurrentflowand voltageswitching,whichisperformedbytransistors,QCA usesthepositionalorderofelectronsinnanoscalequantum dotstoencodebinaryinformation.Oneexampleofanactual QCA cell is a four-quantum-dots system filled with two electrons;Coulombicrepulsioncausesthepairofelectrons tobeintwoenergystablediagonalstates,whicharelogic states0and1.Thepropagationofinformationisbasedon electrostaticinteractionbetweenneighboringcells,butnot on charge transport, which provides QCA systems with superior degrees of compactness, extremely low power consumption,andthepossibilityofextremelyhighoperating frequencies. The following features of QCA make it an attractivepropositionalcandidatetotheimplementationof futurenanoscaledigitalsystems,inparticulartosequential logic elements, including latches, flip-flops, counters, and shift registers. In this regard, the Universal Shift Register (USR) is an essential element that is greatly used in data transfer, communication systems, and memory access. TraditionalCMOS-basedshiftregistershaveahighnumber oftransistorsandconsumehighamountsofpower,butQCAbasedshiftregistershavefewlogiccells,areducedphysical area,andabetterperformancewithlesspower.Researchers candesign,analyseandoptimiseQCAcircuitswithdesign andsimulationtoolsliketheQCADesigner.Thisfour-stage clocking scheme is unique to QCA that dictates electron tunneling and guarantees an orderly data flow that is essential to the dependable synchronous functioning of sequential circuits as well as the USR. Despite the current issuesofQCAtechnologiesintermsoftheaccuracyoftheir fabrication technique, thermal stability, and scalability of highfabrication rates,there isnowa significant literature showingthatQCA-basedsequentialcircuitsrunfaster,are smaller, and use less energy than CMOS or FinFET-based devices.TheseresultsdemonstratethatQCAcanbecomea verypromisingtechnologyofnextgenerationnanoelectronic systems. The current project is focused at the design and optimization of a Universal Shift Register that is implemented with QCA technology with a systematic comparison between its work and benefits against CMOS/FinFET implementation which ensures the possibilities of QCA as enhancing high-speed low-power futurecomputingarchitecture.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

a) Mistri et al. (2017) TG vs. GDI USR. Mistri et al. make comparisons of 4bit USR designs using TG logic and GDI logic.WithGDPimplementation,thenumberoftransistorsis reduced by 31.5% and area decreases by 29.2%, delay by 26.7%andpowerconsumptionby26.7%.Eventhoughusing CMOStechnology,theworkprovesthatCMOSsimplification oflogiccomponentsincreasessystemUSRefficiency,which isalsoapplicabledirectlytoquantum-dotcellularautomata.

b) Saranya et al.(2013) Low-Power TGMS Flip-Flop USR. ReworkingtheTGMSflip-flopSaranyaetal.haveusedaimed atminimizinginternalcapacitanceandclockloadonlynine transistors reducing internal capacitance and clock load. Their4-bitunit-resolutionscheme(USR)hasareductionin flip-floppowerconsumptionof2.177mwto1.524mwanda matching reduction in the unit-resolution power of their schemeto33.223mwto25.14mW.Thispapershowsthata similar flip-flop architecture has a positive effect on the behavior of sequential circuits, which is especially interesting in the case of quantum-dot cellular automata (QCA)-baseduniversalcomputingregisters

c) JoshiandJangir(2019)BICMOSSISOandSIPORegisters TheauthorsdevelopedBICMOSbasedsingle-input-singleoutput(SISO)andsingle-input-multiple-output(SIPO)shift registers, which combine the energy efficiency of complementarymetal-oxidesemiconductor(CMOS)andthe high-speed of bipolar junction transistors (BJTs). The resultant designs not only have lower propagation delays and a large reduction in power such as the SISO design running at on average 0.549mW or equivalent of 106 uW powercut.Inadditiontothis,theexplorationalsodefinesa principle of location-independent design by the discovery thattheunderlyingflip-floparchitecturecouldbeimproved and the result lead to an immediate performance gain relativetotheperformanceofflip-flopshift-registers;and thenotioncanbegeneralizedtoquantumcellularautomata (QCA).

d) Varunetal.(2025)TSPC+SVLforLow-PowerFlip-Flops. The current design utilizes a 5T true single-phase clock (TSPC) flipflop coupled with a separated variable leakage (SVL)minimizationstrategytobothbuildvariableleakage shift registers that are of significantly higher speed and lower power consumption. The power is reduced successfully to 1.630 to 0.44501171 mW and the propagationdelayisverylowandvariesbetween0.034to 0.35ns.Theseresultshighlightthefactthatimprovingclock architecture and reducing the number of transistors is an effective way to improve the performance of a sequential circuit, which is important in the design of QCA universal shiftregisters.

e) Pattanaik&Samal(2018)Pulse-LatchBasedUSR.Here, the authors replace traditional flip-flops with Static Sense Amplifier Shared Pulse Latches (SSASPL) and PTL-based

multiplexers to apply them in the creation of a 4-bit UniversalShiftRegister(USR)whichisrathercompact.This architecturalchangeimpliesa4-folddecreaseinthenumber of transistors used in the design 216 92, a 532 ps propagation delay reduction to 324 ps, and a subsequent reduction in the dynamic power drawn. The suggested reduction in storage components and pulse-based functionality is consistent with the revolution of effective Quantum-dotCellularAutomata(QCA)design.

f) Sanadhya & Sharma (2025) Adiabatic Logic Shift Registers.Theauthorscameupwitha4-bitShiftattheultralow-powerarchitectureusingDC-DBPFALadiabaticlogic. By as much as 85 per cent power is saved, and the PIPO register uses a dissipation of 0.026mW when a 45nm technologynodeisused.Theconceptofenergyrecoveryand energy minimisation of switching can be compared to the clock gated, low energy consumption of quantum-dot cellularautomata(QCA).

g) Isukapatla & Mala (2016) FinFET + SVL SISO Register. They designed a 5T TSET FinFET flip-flop using SVL to significantly decrease the amount of leakage that occurs duringshiftregisteroperations.Thetotalamountofpower decreasessignificantly(CMOS:1.486µW→FinFET+SVL: 0.231µW).Thisstudydemonstratesthatleakageshouldbe minimizedandthatstoragecanalsobesimplifiedtoimprove efficiency,whichparallelsthereductionofswitchingenergy inQuantumCellularAutomata(QCA).

h) Gurumurugan et al. (2017) FinFET + SVL for SISO/SIPO/PISO/PIPO. The authors applied Universal Single-Stage Voltage-Level Converter (U-SVL) and LowVoltageLevelShifter(L-SVL)powergatingtoFinFET-based TSET flip-flops in order to reduce standby leakage in all types of shift-registers, with the SISO type exhibiting the lowest overall power consumption compared to its CMOS counterparts. The fundamental principle behind this approach is to eliminate unnecessary leakage and transitions a concept that will be important when optimizing the functionality of a Universal Shift Register (USR)inQCA.

i) Hajare (2022) MOSFET vs FinFET Datapath Circuits. HajareassessesMOSFETandFinFETdatapathcircuitryat various technology levels, and concludes that FinFETs greatlyoutperformMOSFETsbecauseoftheirsignificantly lower SCEs. FinFET-based designs have shown both decreaseddelay(aslowas8.93ps)andhavebeenableto run on nanowatts of power, while MOSFET designs failed before they were scaled down to 45nm. Therefore, the results support nanoscale design optimizations which are applicabletoQCAUSRs.

j) D’Aniello et al. (2025) SEU Effects in 16 nm FinFET Registers.Theauthor’stestedtheSingleEventUpset(SEU) behavior of a 150-bit FinFET shift register subjected to heavy-ionirradiation.Theauthor’sfoundthattheSEUcross-

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

sectionsforthe150-bitshiftregisterswereverylow(~10-9 cm2/bit),howevertheauthorsalsofoundthattheTMRwas unabletomitigateerrorsresultingfrommultiplebitupset events created by the tight device spacing in the dense nanoscale designs used in this experiment. Therefore, the authors'findingsdemonstratethatdensenanoscaledesigns willberequiredtoimplementnewformsoferrormitigation; anareadirectlyrelatedtothehigh-densitynatureofmany QCAcircuitimplementations.

k) Karthika and Krishnaveni (2023) QCA-Based Universal Shift Register Using Majority Logic and D Flip-Flops. In response to CMOS technology limitations, Karthika and Krishnavenidevelopeda4-BitFullAdderandUniversalShift Register (USR) based on Quantum-Dot Cellular Automata (QCA). A QCA-based USR that utilizes Majority Gates, Inverters and a QCA D-Flip-Flop along with four-to-one multiplexerssupportsleft/rightshifts,"hold"and"parallel load". Simulations in QCADesigner confirm that logic is correctlyperformed,thatpolarizationofthecellsisstable andthatthereiszonesynchronizedclocking.Comparedto traditionalCMOSimplementations,theauthorsreportthat theirdesignuseslessarea,haslowerlatencyandconsumes nearly zero power. The authors also address QCA implementation layout issues and describe an automated layouttoolfordevelopinglarge-scaleQCAcircuits.

l) Padma Selvi & Shyni (2017) QCA-Based Frequency DividerDesignUsingT,D,andJKFlip-Flops.PadmaSelviand Shyni (2017) introduce frequency dividers based on QCA, which are constructed with T, D, and JK flip-flops, and overcomeCMOSdrawbacks,suchasleakageandscaling.The majority logic and model layouts are developed in QCADesigner to develop each flip-flop. The proper functioningofthedividingbytwoischecked,andTflip-flop hastheminimalarea(102cells,0.12µm²).Theexperiment showsthatthecomplexityofflip-flopshasadirectinfluence ontheQCAareaandthenumberofcells.Althoughitfocuses on dividers, the work provides useful information on the designofQCAflip-flops,clocking,andsequentialbehavior, whichisneededinthedesignofQCA-basedUniversalShift Registers.

m) Nagul (2021) Design and Simulation of a QCA NanoCalculator for High-Speed Arithmetic Operations. Nagul (2021) implements a nano-calculator with QCA, demonstrating that QCA is a promising post-CMOS technology,asithasaverylowpowerconsumption,small size,andahighspeed.ThepaperdescribesthebasicsofQCA includingcellstructure,majoritygates,cross-oversofwires, andfour-phaseclocking,andthenappliesarithmeticunits such as adders, subtractors, multipliers, and dividers. SimulationusingQCADesignertoverifycorrectfunctioning andstable propagation ofclock zones. Thoughfocused on combinationallogic,theworkprovidesimportantinsights intoQCAdesign,clocking,andlayouttechniquesrelevantfor buildingyourQCA-basedUniversalShiftRegister.

n) ChakrabartyandKhan(2013)suggestanoptimizedand fault-tolerantQCAinverterdesignwithminimumnumberof cells.Theauthorsreducethetraditional11-cellinvertertoa compact3-cellversionbutimprovereliabilitybyextendingit toa5-cellstructurewithnear-idealpolarization(±0.994). Increasingthenumberofinteractingcellsimprovesstability and lowers defect susceptibility, according to kink-energy analysis.Theoptimizedinvertershowsanoptimizedarea,a better fault tolerance and a better polarization than conventional designs. This work is valuable for QCA sequential circuits including QCA-based USRs where robust inverters directly impact performance and layout density.

o) Jeon (2023) presents advanced multi-layer QCA shift registersforlow-energyLFSRoperationsincryptographic systems.ThestudylooksforlimitationsinpreviousQCASR designsconsistingofheavyuseofmajoritygates,complex wiring,andhighamountsofenergydissipation.Tosolvethis, the author introduces multi-layer SISO and PIPO SR using simple interaction-based D-latches, which improve the modularity and reduce the crossover overhead. QCADesigner/Esimulationsdemonstratemorethan27%of area-time performance and as much as 65% of energy dissipationreduction.TheworkisusefulforQCA-basedUSR design, and provides the scalable, low-energy and layoutefficientsequentialstructuresthatcanbeapplieddirectlyto yourproject.

AcrossallofthereviewedpapersonthetopicofCMOSand FinFET, it is clear that traditional transistor-based technologiesarehittingphysicallimitsbecauseofleakage, short-channel effects, high power density, and reduced reliabilityinnanoscalenodes.Evenadvancedsolutionssuch as FinFETs exhibit sensitivity to radiation, increased multiple-bit upsets, and a lack of stability as device dimensionsdecrease.

On the other hand, QCA literature consistently shows advantages such as ultra-low power, high device density, compact layouts, faster operation, and efficient sequential building blocks (flip-flops, latches, multiplexers, shift registers, etc.). However, the QCA papers also highlight major challenges such as clocking complexity, wire crossovers,faultsensitivity,lowlevelofdesignautomation, energy dissipation in long wires, and scalability issues in olderQCAshiftregisterarchitectures.

Although several QCA works optimize individual components (inverters, flip-flops, shift registers, nanoarithmeticunits,etc.),thereisstillnoresearchthatpresents a fully optimized Universal Shift Register (USR) that is modular, energy-efficient, multi-mode (SISO/SIPO/PISO/PIPO), and directly comparable with modernCMOS/FinFET-basedUSRs.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

Therefore,basedontheexistingliterature,thereisaclear research gap: there is no unified, optimized, and scalable QCA-based Universal Shift Register that not only outperformsCMOS/FinFETUSRsbutalsoovercomesQCAspecific challenges such as clock alignment issues, energy dissipation,andlayoutcomplexity.

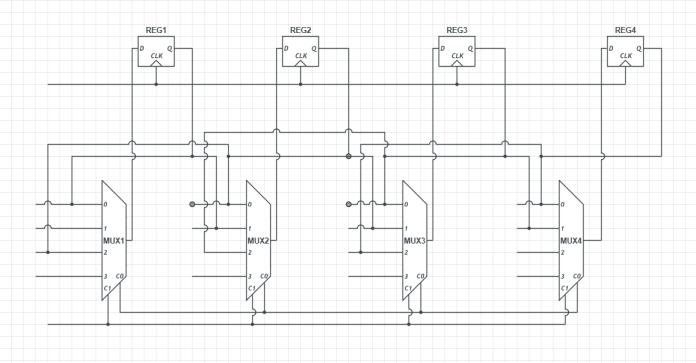

Circuit Diagram of a Universal Shift Register in (Fig 1.1) designed in Circuit Lab shows a proper idea of building blockstodesignedQCALayout.

Fig -1:UniversalShiftRegisterusing4:1MuxandD-Flip Flop

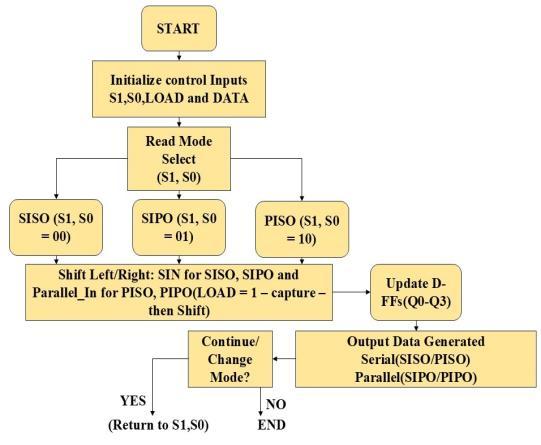

IntheabovecircuitdiagramthebasicbuildingblocksofUSR are given and it perform all 4 operations such as SISO,SIPO,PIPO,PISO (also known as shift and load operations). The S0 and S1 are control lines for the USR based on the logic behind these two control lines output takesplace.TheFlowdig.fortheoperationisalsoshownin Fig1.2.

Fig -2:FlowDiagramforUniversalShiftRegister

The Universal Shift Register (USR) operates through four distinctmodesdeterminedbythecontrolsignalsS1andS0, allowingseamlessswitchingbetweenserialandparalleldata transfers. The register begins by initializing key control inputssuchasS1,S0,LOAD,andtheserialandparalleldata

lines, after which it remains idle until a specific operating modeisselected.Oncethecontrollinesareconfigured,the mode of operation is automatically identified: 00 enables Serial-InSerial-Out(SISO),01enablesSerial-InParallel-Out (SIPO), 10 enables Parallel-In Serial-Out (PISO), and 11 enablesParallel-InParallel-Out(PIPO).Thisflexiblemapping ofcontrolsignalsallowsasingleUSRarchitecturetohandle both gradual bit-by-bit shifting and full data transfers simultaneously,dependingonapplicationrequirements.

During execution, the register performs data movement according to the selected mode. In SISO mode (00), each incomingserialbitpropagatesslowlythroughtheflip-flop chainwitheveryclockpulseuntilitreachestheoutputstage, ensuringbothinputandoutputremainstrictlysequential.In SIPO mode (01), bits enter one after another via a single serial input but are stored internally across multiple flipflops;onceshiftingiscomplete,thefullsetofvaluesbecomes instantly available on parallel output lines. Conversely, in PISO mode (10), the LOAD signal enables the full block of inputdatatoentertheregistersimultaneously,afterwhich LOADisdisabledandclockpulsesbeginshiftingthestored bits outward one at a time through a single serial output. Finally,inPIPOmode(11),activatingtheLOADsignalplaces all input data directly into every flip-flop at once, and because shifting is unnecessary, the complete dataset appearsimmediatelyontheparalleloutputlines.

Afteranyofthefouroperations,theflip-flopcontentsupdate according to the shifting or loading that has taken place, whichdetermineswhethertheoutputemergesseriallyover time or parallelly all at once. The system then verifies whetheranotheroperationisrequired,andifso,itreturnsto mode-selectionbyadjustingS1andS0.Ifnofurthershifting or loading is requested, the process halts. By dynamically reconfiguringbehaviorbasedonthecontrolsignalsrather thanhardwaremodification,theUSRintegratesSISO,SIPO, PISO, and PIPO capabilities within the same structural design.ThismakesitahighlyversatilecomponentinQCAbased systems, capable of supporting linear bitstream processing as well as simultaneous multi-bit transfers for efficientdatahandling.

Fromthereviewed research papersrelatedtothevarious results of the research papers on the different field of technology that are done by using the various types of transistors such as the Complementary Metal Oxide Semiconductor(CMOS),FinFieldEffectTransistor(FinFET) andtheQuantumCascadedAlloy(QCA)itisclearthatthe traditionaltransistortechnologiesarereachingthephysical limitandtheperformancelimitduetothescalingchallenges, highleakage,powerdissipationandreducedreliability.Even advancednodeslike16nm FinFEThaveproblemssuch as SEU vulnerability, increased layout density-induced faults andincreaseddesigncomplexity.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

Ingeneral,Quantum-dotCellularAutomata(QCA)becomesa promisingpost-CMOSoptionduetoitsextremelysmallcell size,ultra-lowpoweroperation,highdensityandhighspeed switchingbasedonelectronpolarizationratherthancurrent flow. Research on QCA flip-flops, multiplexers, inverters, multi-layer shift registers and nano-arithmetic circuits , showsreducedarea,lowerenergydissipation,easierrouting andbetterperformancecomparedtothedesignsofthesame circuitinthefieldofCMOS/FinFET.However,QCAresearch also shows that there are difficulties like clocking synchronization,crossoverdesign,layoutsensitivityanda lackofstronglarge-scaleautomationtools.

Basedonthesefindings,theobjectiveofthepresentworkis to design and implement an optimized Universal Shift Register(USR)withQCAtechnologytakingadvantageof:

•majority-logicprimitives,

•low-energyQCAclocking,

•compactsequentialelements,

•multi-layerandoptimizedroutingstrategies.

ThegoalistohaveaUSRwhichissmaller,fasterandmore energy-efficientthanthecorrespondingcounterpartsusing the more energy-efficient option, but also mitigate design limitationsdiscoveredinpastQCAliterature.Thisworkis intended to make a contribution to scalable, low-power nanoscale sequential circuits that can be used for future high-densitycomputingsystems.

[1] R. K. Mistri, R. Ranjan, P. Prasad, and A. Anupriya, “IC Layout Design of 4-bit Universal Shift Register using Electric VLSI Design System,” Int. J. Eng. Res. Technol. (IJERT), vol. 6, no. 04, Apr. 2017, DOI: 10.17577/IJERTV6IS040320.

[2] M. Saranya, V. Vijayakumar, T. Ravi, and V. Kannan, “Design of Low-Power Universal Shift Register,” Int. J. Eng. Res. Technol. (IJERT),vol.2,no.02,Feb.2013,DOI: 10.17577/IJERTV2IS2551

[3] N.JoshiandR.Jangir,“Low-Power,High-SpeedSISOand SIPOShiftRegistersusingBiCMOSLogic,”(2019).

[4] Varun, S. et al., “True Single-Phase Clock (TSPC) FlipFlopandShiftRegisterDesigns ComparativeStudy,” (2025).

[5] S.PattanaikandS.Samal,“DesignAlternativesfora4-Bit UniversalShiftRegisterUsingClockPulseSenseLatch,” (2018),DOI: 10.13140/RG.2.2.35366.96323

[6] S.SanadhyaandS.Sharma,“DC-DBPFALAdiabaticLogic forLow-PowerShiftRegisters,”(2025).

[7] K.IsukapatlaandS.Mala,“FinFET-basedTSETDFlipFlop and SVL Techniques for Low-Power Shift Registers,”(2016).

[8] R.Gurumuruganetal.,“FinFETShiftRegisterswithSVL Power-GatingforLeakageReduction,”(2017).

[9] S. A. Hajare, “Performance Evaluation of Datapath Designs using MOSFET and FinFET Technologies,” (2022).

[10] F. D’Aniello, M. Tettamanti, S. A. A. Shah, and A. Baschirotto, “Single-Event Upset Characterization of a Shift Register in 16 nm Bulk FinFET Technology,” Electronics, vol. 14, no. 7, 2025, DOI: 10.3390/electronics14071421.

[11] K. Karthika and M. Krishnaveni, “4-Bit Full Adder and UniversalShiftRegisterDesignusingQCA,”(2023).

[12] J. Padma Selvi and P. Shyni, “Utilization of QCA Based FlipFlopstoDesignFrequencyDividers,” Int. J. Adv. Res. Trends Eng. Technol.,vol.4,SpecialIssue10,Mar.2017.

[13] S. Nagul, “Quantum Dot Cellular Automata (QCA) NanoCalculator,” Int. J. All Res. Educ. Sci. Methods,vol.9, no.12,Dec.2021.

[14] R. Chakrabarty and A. Khan, “Design of a Fault-Free Inverter Circuit using Minimum Number of Cells & Related Kink Energy Calculation in QCA,” in Proc. Int. Conf. Computation and Communication Advancement (IC3A),Kalyani,India,2013,pp.369–373.

[15] J.-C.Jeon,“Multi-LayerQCAShiftRegistersandWiring StructureforLFSRinStreamCipherwithLowEnergy Dissipation in Quantum Nanotechnology,” Electronics, vol. 12, Article 4093, 2023.DOI: 10.3390/electronics12174093 (you can verify on publisher’ssite).