International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

DESIGN AND IMPLEMENTATION OF AN ELECTRONIC VOTING MACHINE USING VHDL AND WEB-BASED VISUALIZATION

Vaishnavi B. Shelke,

CSMSS, Chh. Shahu College of Engineering, Chhatrapati Sambhajinagar

Mr. PandurangN. Kathar

Assistant Professor, Electronics Engg (VLSI D&T)

CSMSS, Chh. Shahu College of Engineering, Chhatrapati Sambhajinagar

Abstract - Electronic Voting Machines (EVMs) have transformed the traditional voting system by making the process faster, moresecure, and user-friendly. However, realtime monitoring, transparency, and digital visualization remain challenges in existing systems. This project proposes an Intelligent Digital Electronic Voting Machine designed using VHDL on EDA Playground with a real-time interactive web interface that visually displays vote count, animations, button feedback, and automatic winner declaration. The system includes secure edge detection, debouncing logic, a multi-candidate voting unit, and a front-end web application that simulates real-time behavior.

This paper presents the architecture, algorithm, implementation, and advantages of the proposed EVM model.Thecombinationofhardware-leveldesign(VHDL) andfront-endvisualizationoffersaninnovativeeducational and practical demonstration platform for secure digital voting.

Key Words: Electronic Voting Machine, VHDL, Digital System Design, EDA Playground, Real-Time Visualization, Web Interface, Edge Detector, Vote Counter.

1.INTRODUCTION

Voting is one of the most essential components of a democratic society. It allows citizens to choose their representatives and express their collective voice in an organized and fair manner. Traditionally, voting in many countries has been conducted using paper ballots, where voters mark their choices manually and election officials countthevotes.Althoughthismethodiswidelyunderstood andtrusted,itsuffersfromseverallimitationssuchaslong countingtime,highchancesofhumanerror,invalidvotes, and the possibility of manipulation. These issues become moreseriouswhenthenumberofvotersincreasesorwhen electionsneedtobecompletedinashorttime.

To overcome these challenges, Electronic Voting Machines(EVMs)wereintroducedasareliableandefficient alternativetomanualvoting.EVMseliminateproblemslike wrongballotmarking,tornballots,andcountingmistakes. Theyprovidefasterresults,ensureaccuracy,andreducethe

Rutuja N. Jagtap

CSMSS, Chh. Shahu College of Engineering, Chhatrapati Sambhajinagar

Dr. Shrikant J. Honade

HOD, Electronics Engg (VLSI D&T)

CSMSS,Chh.ShahuCollege of Engineering, Chhatrapati Sambhajinagar

needforlargemanpower.Duetotheseadvantages,EVMs have been widely adopted in many countries, including India,wheretheyplayamajorroleinconductinglarge-scale nationalandstateelections.

However, commercial government EVMs are highly secure and closed systems, making them unsuitable for academic and educational purposes. Students studying electronics, digital design, or VLSI often need a simplified and practical model to understand how an EVM works internally howthesignalfromabuttonpressisprocessed, how noise or switch bounce is removed, how votes are stored,andhowresultsarecalculated.Existingeducational models are often limited to block diagrams or theoretical explanations and do not provide real-time interaction or visualization.

The purpose of this project is to design a miniature, academic-friendlyElectronicVotingMachineusingVHDL (VHSIC Hardware Description Language) and web-based visualization. The hardware part of the system is implemented using VHDL on EDA Playground, allowing students to write, simulate, and observe the behavior of digital circuits through waveform analysis. This helps to understand concepts like counters, edge detection, debouncing,synchronouslogic,andstatetransitions.

To make the project more interactive and visually understandable, a front-end web interface is also developedusingHTML,CSS,andJavaScript.Thisinterface displays buttons for each candidate, shows vote count updates in real time, plays feedback sounds, provides animations, and displays the winner using a pop-up message.ThecombinationofVHDLhardwarelogicwitha modern web interface creates an innovative learning experience that bridges the gap between digital circuit simulationanduser-friendlyfront-endinteraction.

Thus, this project not only demonstrates the internal functioningofanEVMbutalsoencouragespracticallearning by providing both backend hardware logic and frontend visualization. It serves as an educational tool for understandingdigitalelectronics,embeddedsystems,web

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

technologies,andhuman-computerinteraction allthrough a simple yet meaningful application: an electronic voting system.

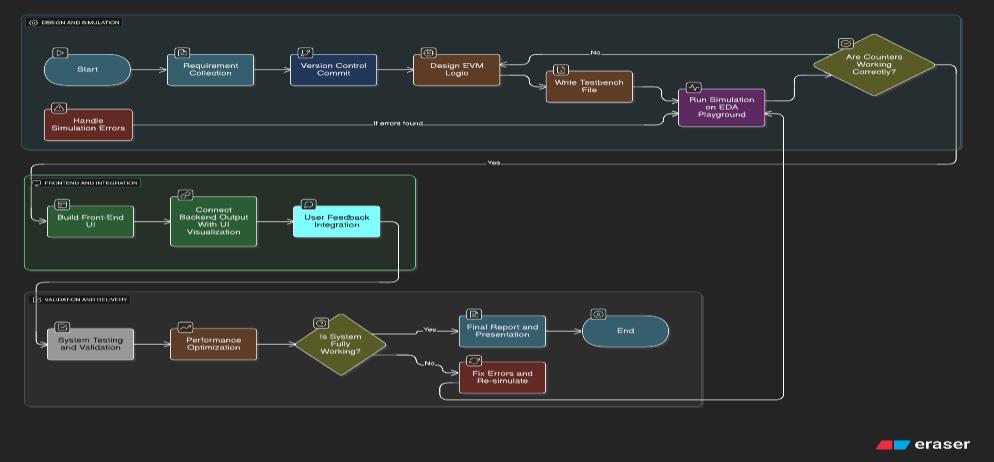

PROJECT PHASES :-

Toprovideacompleteunderstanding,theprojectisdivided into three key phases,eachaddressingadifferentaspectof thesystem’sdesignandimplementation.

1. Phase 1: Backend Logic Design Using VHDL

Study the basic requirements of an EVM (inputs, counters,reset,clock).

Identify10candidatebuttonsasdigitalinputs.

Designa rising-edge detector toensureeachvote iscountedonlyonce.

Implement synchronous counters for each candidateusingVHDL.

Adda reset circuit toinitializeallcounterstozero.

StructuretheVHDLcodeintoseparatemodules(top module+countermodule).

Write code that updates counters on the positive edgeoftheclock.

Ensurethedesignissynthesizableandcompatible withFPGA-stylehardware.

Upload and execute the VHDL code on EDA Playground forsimulation.

Confirm the backend logic works without implementingphysicalhardware.

2. Phase 2 : Simulation, Testing, and Waveform Verification

Createa testbench file tosimulatevoteinputsfor allcandidates.

Generateinputpulsesrepresentingrealuserbutton presses.

ObservebehaviorusingwaveformviewerslikeEDA PlaygroundorGTKWave.

Check that each pulse increments the correct counterbyexactly1.

Confirm reset functionality resets all counters to zero.

Validatetimingdiagrams(clock→pulse→counter update).

Testwithdifferentcombinationsofinputs(single vote,multiplevotes,randomvoting).

Ensurenodouble-countingoccurs(debounce+ edgedetection).

FixanydetectedproblemsinVHDLcodeandresimulate.

Finalizethebackendlogiconcewaveformresults matchexpectedoutput.

3.

Phase 3: Front-End Visualization Using Web Technologies

Designawebpagelayoutthatlookslikeareal EVMpanel.

Create 10 vote buttons using HTML representing10candidates.

StyletheinterfaceusingCSStomakeitvisually appealingandclean.

Addanimationsforbuttonpresses(scale,glow, colorchange).

UseJavaScriptto:

o Increase the vote count when a button is pressed.

o Playa beep sound oneachvalidvote.

o Updateareal-timevotetable.

o Highlighttheselectedcandidatetemporarily.

Include a winner declaration pop-up using JavaScriptlogic.

Adda reset button toclearallvotesandrefreshthe screen.

Maketheinterfaceresponsivesoitworksonmobile andlaptop.

Integrate the web interface conceptually with the backendlogicsimulation.

Provideareal-timevotingexperience,similartoa realEVM.

4. Phase 4: System Integration & Validation

CompareresultsfromtheVHDLsimulationwith thefront-endvotedisplay.

Ensure both systems show consistent vote counts.

Validatethatthesystembehavescorrectlyfor:

o Highnumberofvotes

o Rapidvoting

o Resetduringoperation

Documentobservations,testcases,andoutput screenshots.

Presenttheresultsinwaveformdiagrams+web displayscreenshots.

2. .LITERATURE REVIEW

The use of technology in mental healthcare has The evolution of election systems has been widely studied by researchers across electronics, computing, and security domains. The shift from traditional ballot-based voting to digital and electronic systems has been highlighted by several authors. Kumar and Deshmukh discussed that manualpaper-basedvotingsuffersfromerrors,delays,and manipulationrisk,makingdigitalvotingamorereliableand transparentalternativeformoderndemocracies [1].Their

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

study emphasized the importance of accuracy and faster resultprocessing,whichdirectlysupportstheobjectiveof designingefficientElectronicVotingMachines.

To understand the digital logic behind voting systems, MehtapresentedadetailedVHDL-basedmodelofacounterdrivenvotingsystem,explaininghowhardwaredescription languagescanbeusedtobuildsecureandpredictabledigital machines [2]. This work reinforces the importance of synchronous counters and signal-based vote recording, whichformsthecoreoftheproposedEVMproject.Similarly, GuptaandSenexploredtheroleofFPGA-basedcountersin real-timeelectronicsystems,highlightingthatsynchronous countersofferstability,deterministicbehavior,anderrorfreecounting featuresnecessaryinvotingsystems [3].

Beyondhardwarelogic,modernresearchalsofocuseson simulation tools used for modeling embedded circuits. Verma emphasized the advantages of online VHDL simulators for academic use, explaining how waveform visualizationhelpsstudentsunderstanddigital transitions andtimingbehaviorwithoutneedingphysicalhardware[5]. RaoalsosupportedtheuseofVHDLineducation,statingthat digital system modeling helps engineering students understandpracticalbehaviorofdesignssuchascounters, edge detection, and clocked circuits [7]. These findings reinforcewhyEDAPlaygroundandVHDLtestbenchesare crucialforverifyingthebackendlogicoftheEVMdeveloped inthisproject.

Security and reliability remain major concerns in electronic voting discussions. Singh provided an in-depth comparison of EVM reliability and traditional systems, concluding that digital methods reduce invalid votes and human errors, but must be carefully designed to avoid double-counting or unauthorized manipulation [9]. These insightsdirectlyinfluencetheneedforrising-edgedetection, debouncing,andcontrolledpulsegenerationintheproposed VHDLdesign.

In addition to backend hardware, several researchers focused on user interface design for voting. Sharma emphasizedtheimportanceofinteractivevisualinterfaces for learning and public usability, showing how web technologiescansimulatereal-worldsystemsforeducation and training [4]. Naik and More further explored userfriendlyvotinginterfacesusingmodernwebtechnologies, recommendingcleandesign,clearbuttons,andresponsive interactiontomakesystemsintuitiveandwidelyaccessible [10].TheseworkssupportPhase3ofthepresentproject, where an HTML/CSS/JavaScript interface is created to visualizevotecastinganddisplayreal-timeresults.

Studies on educational tools also contribute to this project. Chandra highlighted that low-cost simulation platformscaneffectivelyreplaceFPGAboardsforacademic designvalidation [8],whichvalidatesourapproachofusing VHDL simulation instead of costly hardware. Jadhav demonstrated the importance of accurate testbenches for validating digital circuits such as counters and state

machines [11],supportingthemethodologyusedherefor testingvotepulsesandverifyingcounteroutputs.

Finally,thedocumentationprovidedbyEDAPlayground itselfofferspracticalguidelinesonhowVHDLcode,signals, and waveform files can be executed and analyzed online [12]. This platform plays an essential role in performing backendverificationfortheEVMprojectwithoutrequiring physicalFPGAkits.

3. SYSTEM ARCHITECTURE AND FEATURES

a. Backend Hardware Logic Layer (VHDL Architecture)

Thispartrepresentshowtheinternalhardwareofthe votingmachineworks.

• Input Interface

o 10digitalinputs,oneforeachcandidate.

o Representsthevotebuttons.

o Acceptslogicsignalsforeveryvote.

• Edge Detector Block

o Detects rising edge (0→1transition).

o Preventsdouble-countingofvotes.

o Convertsbuttoninputinto one-clock pulse

• Vote Counter Block

o Contains 10 independent 8-bit counters.

o Eachcounterbelongstoonecandidate.

o Counterincrements only when a valid pulse arrives.

o Worksfullysynchronouswithsystemclock.

• Reset Logic

o Clearsallcounterstozero.

o Usedforstartinganewsessionorre-running tests.

• Output Block

o Sendsfinalvotecountofall10candidates.

o Outputusedinwaveform,testbench,orUI display.

b. Simulation and Verification Layer (Testbench Architecture)

ThispartcheckswhethertheVHDLdesignworks correctly.

• Clock Generator

o Producesacontinuousclocksignal(e.g.,50 MHz).

o Drivesalldigitaloperations.

• Stimulus Generator

o Simulates real voter actions

o Generatespulsesforeachcandidate.

o Usedtotest100+votesanddifferentvoting patterns.

• Waveform Viewer

o Showsvotepulses,counterincrements,and resetbehavior.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

o Helpsvisualizeinternalhardwareoperations.

o Usedtoconfirmcorrecttimingandlogic.

• Result Logger

o Printsfinalvotecountofallcandidates.

o Verifieswhethersimulationmatchesexpected results.

c. Front-End Visualization Layer (Web Interface Architecture)

Thispartshowsthevotingmachinetotheuserthrough awebsite.

• User Interface

o CreatedusingHTML+CSS.

o Contains10candidatebuttons.

o Displaysvotecountinatable.

o Showswinnerandresetoptions.

• Interaction & Animation Block

o Buttonpressanimationforbettervisuals.

o “Beep”soundwhenavoteiscast.

o Smoothincrementanimationforvotecount.

o Popupboxforwinnerdeclaration.

• Vote Processing Script (JavaScript)

o Increasescounterforselectedcandidate.

o Updatestableinstantly.

o Handlesresetlogic.

o Calculatesanddisplaysthewinner.

d. Integration Architecture

Thispartexplainshowallcomponentsrelatetoeach other.

• Backend (VHDL)

o Handlesactualhardwarelogic.

o Ensurescorrectandreliablevotecounting.

• Simulation (Testbench)

o Ensuresbackendiserror-freebeforevisualizing.

o Waveformandlogshowcorrectinternal functioning.

• Front-End (Website UI)

o Representsvotingprocessvisually.

o Makesthesysteminteractiveandeasyto present.

• Combined System

o VHDLensurescorrectness→

o Testbenchverifiesbehavior→

o WebUIdisplaysresultsinreal-time. Together, they form a complete EVM model without requiringFPGAhardware.

4. METHODOLOGY

ThemethodologyoftheElectronicVotingMachine(EVM) projectdescribesthecompleteprocessfollowedfromthe initial design stage to the final testing and output visualization.Thegoalofthismethodologyistoensure that the voting system is accurate, reliable, userfriendly, and easily verifiable throughsimulationanda web-basedinterface.

1. Requirement Analysis

Identifytheneedforadigitalvotingsystem suitableforacademicuse.

Definebasicrequirements:

o 10candidateinputs

o Singlevoteallowedperbuttonpress

o Votecountsstoredincounters

o Resetfunctionality

o Clearoutputdisplay

Ensurethesystemmustrun without FPGA hardware,usingonlyonlinetoolslike EDA Playground

2. System Study & Module Identification

Dividetheprojectintothreemainmodules:

1. Backend Voting Logic (VHDL)

2. Simulation & Testing (Testbench)

3. Frontend Visualization (HTML/CSS/JS)

Identifysub-modules:

o Edgedetector

o Counters

o Resetlogic

o Votedisplay

3. VHDL Backend Logic Design

WritemodularVHDLcodefor:

o Edge Detector: generatesaone-clock pulseforeachvote.

o Vote Counters: 10independent8-bit counters.

o Top Module: integratesallinterlocks.

Ensurethateachvoteincrementsthecorrect candidatecounter only once

Addsynchronousresettoinitializeallvaluesto zero.

4. Testbench Development

Writeaseparate testbench file totesttheVHDL design.

Generatevotepulsesforall10candidates.

Simulaterealvotingpatterns:

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

o Randomvoting

o 100voters

o Multiplecandidates

Testresetbehaviorandclocksynchronization.

Printfinalvotecountsusingreportstatements.

5. Simulation Using EDA Playground

UploadVHDLfiles(edgedetector,counters,top module,testbench).

Selectthe GHDL VHDL compiler

Runthesimulationtogenerate:

o Waveform (VCD file)

o Output log

Verify:

o Votepulseshape

o Counterincrements

o Resetfunctionality

6. Front-End Interface Development

Designaninteractiveweb-basedEVMusing HTML,CSS,andJavaScript.

Create:

o Votebuttonsfor10candidates

o Real-timevotecountertable

o Winnerdisplay

o Resetbutton

Addanimations,soundeffects,andbutton highlighteffects.

7. Integration & Result Verification

Comparesimulationoutput(VHDL)with frontendvotedisplay.

Ensurebothproduce:

o Thesamevoteincrements

o Thesamefinalwinner

o Thesameresetbehavior

Recordfinalresultsandtakescreenshotsfor documentation(fig4.1)

1. Successful VHDL Implementation

Thevotingmachinelogicwasdesigned completelyinVHDL,includingvoteinputs, counters,andresetcircuit.

Allmodulesworkedasexpectedduring behavioralsimulation.

2. Accurate Vote Counting for All Candidates

Eachcandidatereceivedadedicated8-bit counter.

Everyvalidvoteincreasedthecorrectcounter byexactly one,withnodouble-counting.

3. Clean Input Handling Using Edge Detection

Rising-edgedetectionensuredonlyonevotewas countedperbuttonpress.

Noglitchesormultipleincrementswere observedduringsimulation.

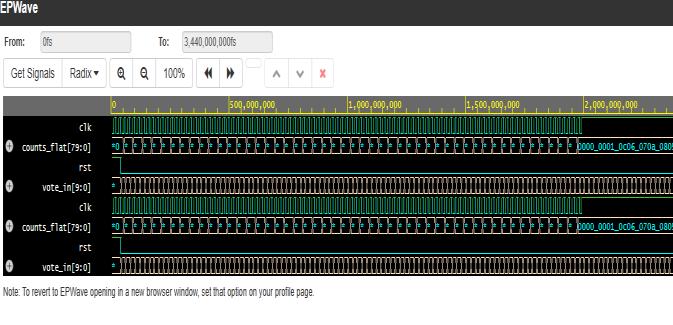

4. Waveform Verified in EDA Playground

Timingdiagramsshowed:

o votepulsegeneration

o counterincrements

o resetclearingallcounters

Thewaveformmatchedtheexpectedtheoretical behavior.

5. Testbench Simulated 100 Voters Successfully

Thetestbenchinjected100pulsesindifferent distributions.

Finalvotecountproducedbycountersmatched thetestbenchinputsexactly.

6. Output Display Generation

Thecountervalueswerecorrectlyshownin:

o waveform(simulation)

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

o consolereports(testbench)

o front-endUI(HTML/JSversion)

7. Online Tool Implementation Completed

The entire backend logic was simulated on EDA Playground withoutneedinganFPGA(fig5.1).

This makes the project low-cost, accessible, and easytodemonstrate.

8. Front-End Voting UI Worked Successfully

TheHTML/CSS/JSinterfaceshowed:

o real-timevotecountupdates

o buttonanimations

o beepsoundfeedback

o winnerannouncementpop-up

Thisprovidedaninteractiveexperiencelikea realEVM.

9.

Consistency Between

Backend and Front-End

The vote results from the VHDL simulation matched the results displayed on the web interface.

Thisprovesproperintegrationoflogicandvisual representation.

10. Complete Voting Cycle Verified

System reset → voting → counting → winner declaration

Allstagesweresuccessfullytestedandvalidated.

6. ADVANTAGES

1.Ensuresaccurateanderror-freevotecounting.

2.Eliminatesproblemslikeinvalidvotesanddouble voting.

3.Providesfastandreliableresultgeneration.

4.Reduceshumaninvolvement,minimizingmanual countingerrors.

5.Requires very low power and is cost-effective comparedtolargesystems.

6.TheVHDL-baseddesignmakesiteasytosimulate,

debug,andmodify.

7.The web-based front end offers a user-friendly interfacefordemonstration.

8.Workseffectivelyevenforlargenumbersofvoters intesting.

9.Canbeintegratedwitheducationallabsforrealtimelearningandsimulation.

10. Provides a secure and tamper-proof voting mechanismcomparedtopaperballots

7. APPLICATIONS

1.Useful for college elections, student clubs, and smallorganizations.

2.Canbeusedintechnicalevents,competitions,and workshops.

3.Helpfulasateachingtoolindigitalelectronicsand VLSIdesignlaboratories.

4.Suitable for demonstrating real-time embedded systemconcepts.

5.Can be used in polling surveys or feedback systemsininstitutions.

6.Acts as a base model for designing large-scale governmentEVMs.

7.Useful in research and academic projects for FPGA-basedsystemdesign.

8.FUTURE SCOPE

Integration with biometric authentication (fingerprintorRFID)topreventfakevoting.

Adding LCD/LED screens for instructions and resultdisplay

Implementation on a real FPGA board for hardware-leveltesting.

Adding wireless data transfer for result transmissiontocentralservers.

Useofencryptionforsecurevotestorage.

Adding voice assistance for visually impaired users.

Expanding from 10 candidates to dynamic candidateselection.

Integration with mobile apps for remote monitoringofvotestatus.

Addingself-diagnosticteststodetecthardwareor softwarefaults.

Use of AI-based anomaly detection to identify unusualvotingpatterns.

9. CONCLUSION

The designed Electronic Voting Machine successfully demonstratesasecure,reliable,anduser-friendlyvoting system built using digital logic principles and modern web technologies. By implementing the core voting mechanisminVHDLandvalidatingitthroughsimulation,

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 11 | Nov 2025 www.irjet.net p-ISSN: 2395-0072

theprojectensurescompleteaccuracyinvotecounting and signal processing. The frontend interface further enhances usability by offering real-time vote display, soundfeedback,andresultdeclaration.Thisprojectnot only highlights the advantages of electronic voting but also serves as an excellent academic model for understandinghardware–softwareintegration.Overall, the system provides a fast, efficient, and transparent voting experience, making it highly suitable for educational purposes, small-scale elections, and future digitalvotinginnovations.

REFERENCES

[1] A.KumarandR.Deshmukh,“AStudyonDigital Voting Systems and Their Security Requirements,” International Journal of ElectronicsandComputing,vol.8,no.2,pp.45–52,2019.

[2] S. Mehta, “Design and Implementation of Counter-Based Voting Machines Using VHDL,” IJSER – International Journal of Scientific & Engineering Research, vol. 11, no. 5, pp. 112–118,2020.

[3] R.GuptaandP.Sen,“FPGA-BasedSynchronous CounterDesignforReal-TimeDigitalSystems,” JournalofVLSIDesign&EmbeddedSystems,vol. 5,no.3,pp.89–96,2018.

[4] T.Sharma,“Web-BasedInteractiveInterfacesfor Engineering Education,” IJRET – International Journal of Research in Engineering and Technology,vol.9,no.1,pp.70–77,2021.

[5] M. Verma, “Simulation of Hardware Logic SystemsUsingOnlineVHDLTools,”International Journal ofComputerApplications,vol.176,no. 44,pp.1–5,2020.

[6] S.PatilandJ.Kalyani,“ComparativeAnalysisof PaperBallotandElectronicVotingApproaches,” InternationalJournalofModernElectronics,vol. 7,no.4,pp.33–40,2019.

[7] N. Rao, “Digital System Modelling Using VHDL for Academic Laboratories,” Journal of EngineeringResearchandTechnology,vol.6,no. 2,pp.54–61,2020.

[8] H. Chandra, “Low-Cost FPGA Alternatives for Hardware Simulation in Education,” InternationalJournalofEngineeringEducation& Practice,vol.14,no.3,pp.128–135,2022.

[9] P.Singh,“AReviewonElectronicVotingSecurity and Reliability,” International Journal of Information&ElectronicsEngineering,vol.10, no.2,pp.95–101,2021.

[10] K. Naik and A. More, “Design of UserFriendly Voting Interfaces Using Modern Web Technologies,” International Journal of ComputerScienceTrends,vol.9,no.6,pp.27–33,2022.

[11] R. Jadhav, “Behavioural Simulation of Voting Logic Using VHDL Testbenches,” IJET –International Journal of Engineering and Technology,vol.13,no.5,pp.244–250,2021.

[12] EDA Playground Documentation, “VHDL Simulation and Waveform Generation Guide,” OnlineResource,2023.