Shifting to 200 mm silicon carbide

200 mm 150 mm

76 mm

100 mm 50 mm

VOLUME 27 ISSUE VII 2021

INSIDE News, Analysis, Features, Editorial View, Research Review and much more

Front Cover CS7 v4RS 5MG.indd 1

@compoundsemi

www.compoundsemiconductor.net

II-VI’S GOLDEN ANNIVERSARY

PROBLEMATIC POINT DEFECTS

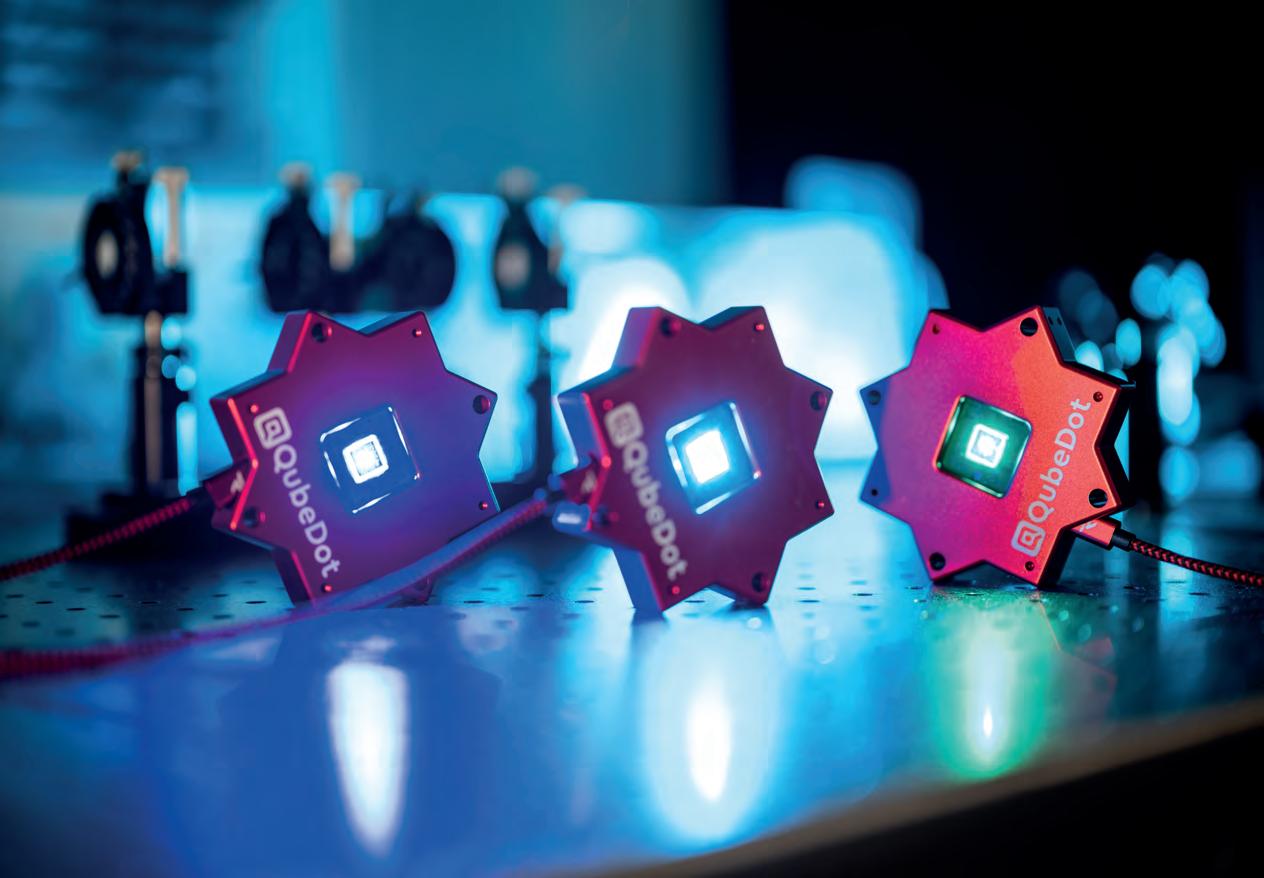

MORE MARKETS FOR MICROLEDS

A candid interview with II-VI co-founder Carl Johnson offers a wonderful insight into the early years

The intrinsic light-quenching point defect is dragging down the efficiency of GaN-based LEDs

Many opportunities beckon for light engines made with microLEDs that vary in pitch, size and wavelength

30/09/2021 10:57