Technology in

context

FPGAs Mix It Up with CPUs

FPGAs Mix it Up with CPUs— The Era of the SoC FPGA The convergence of many factors is enabling a new class of device for the embedded arena. The SoC FPGA combines powerful multicore processing on the same device with an FPGA fabric to optimize parallelism, power consumption and performance. by Chris Balough, Altera

S

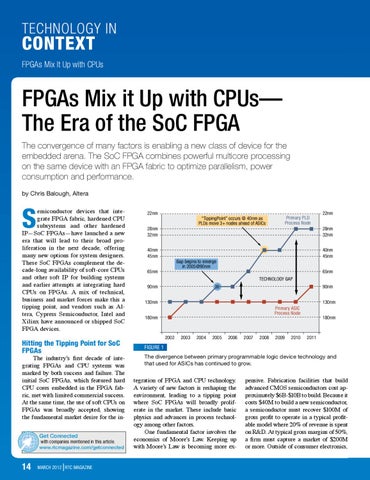

emiconductor devices that inte22nm grate FPGA fabric, hardened CPU subsystems and other hardened 28nm ploration IP—SoC FPGAs—have launched a new 32nm your goal era that will lead to their broad prok directly liferation in the next decade, offering age, the 40nm source. many new options for system designers. 45nm ology, These SoC FPGAs complement the ded products cade-long availability of soft-core CPUs 65nm and other soft IP for building systems and earlier attempts at integrating hard 90nm CPUs on FPGAs. A mix of technical, business and market forces make this a 130nm tipping point, and vendors such as Altera, Cypress Semiconductor, Intel and 180nm nies providing solutions Xilinx havenow announced or shipped SoC ion into products, technologies and companies. Whether your goal is to research the latest FPGA devices.

The industry’s first decade of integrating FPGAs and CPU systems was marked by both success and failure. The initial SoC FPGAs, which featured hard CPU cores embedded in the FPGA fabric, met with limited commercial success. At the same time, the use of soft CPUs on FPGAs was broadly accepted, showing the fundamental market desire for the in-

End of Article Get Connected

with companies mentioned in this article. www.rtcmagazine.com/getconnected

14

22nm 28nm 32nm 40nm 45nm

Gap begins to emerge in 2005@90nm

ation Engineer, or jump to a company's technical page, the goal of Get Connected is to put you 2002 2003 you require for whatever type of technology, the Tipping Point for SoC and productsHitting you are searching for. Figure 1

FPGAs

Primary PLD Process Node

“TippingPoint” occurs @ 40nm as PLDs move 3+ nodes ahead of ASICs

65nm TECHNOLOGY GAP 90nm 130nm Primary ASIC Process Node

2004

2005

2006

2007

2008

2009

2010

180nm

2011

The divergence between primary programmable logic device technology and that used for ASICs has continued to grow.

tegration of FPGA and CPU technology. A variety of new factors is reshaping the environment, leading to a tipping point where SoC FPGAs will broadly proliferate in the market. These include basic physics and advances in process technology among other factors. One fundamental factor involves the economics of Moore’s Law. Keeping up with Moore’s Law is becoming more ex-

MARCH 2012 RTC MAGAZINE

Get Connected with companies mentioned in this article.

pensive. Fabrication facilities that build advanced CMOS semiconductors cost approximately $6B-$10B to build. Because it costs $40M to build a new semiconductor, a semiconductor must recover $100M of gross profit to operate in a typical profitable model where 20% of revenue is spent on R&D. At typical gross margins of 50%, a firm must capture a market of $200M or more. Outside of consumer electronics,